# **EUSO CHIP STATUS REPORT**

EUSO electronics meeting 5-6 March 2001 - GENOVA

Paolo Musico - INFN Genova

Paolo.Musico@ge.infn.it

- Architecture of EUSO chip PERSEO

- Technology and tools

- Prototype test chip

- Future plans

## PRELIMINARY SPECIFICATIONS FOR THE EUSO FRONT END CHIP

- Reference document: "AIRWATCH FROM SPACE"

- ✓ 64 channels chip. Mapping one to one with the R5900-M64 PMT anodes

- ✓ On chip circular memory buffer

- Serial interface for working parameters configuration

- ✓ Power budget: about 1 mW/ch

- ✓ Single photon double pulse resolution: ≈10 ns (≤ 20 ns)

### SINGLE CHANNEL LOGIC

Mask after the discriminator to disable noisy pixels

8 bit programmable down counter with async reset/reload Tck = 10 ns

Outputs to generate row column and timing signals

**Pixel** PROGR. wired-OR X COUNTER detector wired-OR Y set single photoelectron threshold GTU reset

Possibility to have a low resolution timing information (50-100 ns)

Additional outputs for local trigger logic?

to wired-OR macrocell timing channel

#### PERIPHERY LOGIC

SRAM memories to store rows, column (and timing) data

Address generator: UP/DOWN counter

Bus steering logic for reading/ writing memories

High speed timing output

n pixels wired or

n x n pixels Macrocell

to timing and counting channel

X wired or pixels

To data compression and telemetry

n x 2 k PAM

12 bits up/down counter address generetor

The global OR can be done with the last dynode signal, using a 65<sup>th</sup> channels identical to the others (more or less).

Local trigger logic?

#### TECHNOLOGIES AND TOOLS

- ✓ AMS 0.35 µm, 2 Poly 3 Metal 5V I/O, available through EuroPractice chosen for the test chip and suitable for the final chip design care for Latchup and SEE problems

- ✓ IBM 0.25 µm, 1 Poly 5 Metal 2.5V I/O, available through RAL RAD hard standard cell library design rules for RAD hard analog circuits (enclosed gate MOS) used by CERN groups for LHC experiments

Both technologies have design kits for CADENCE v 4.4.3, Synopsys, Verilog, Spectre (AMS), Hspice

#### PROTOTYPE TEST CHIP

- ✓ Test of different kinds of preamp-discriminator pairs (Fabio).

- ✓ Test of voltage and current reference circuits.

- ✓ Test of current output DAC used to set up thresholds and biases.

- Test of a simple serial interface to load configuration parameters.

- ✓ Test of small parts of single cell digital circuits (counter, comparator, ...) in order to see how to integrate full custom analog cells with standard cell library blocks.

- ✓ If we'll have time we'll try to put in also some of the periphery logic (SRAM, address generators, ...)

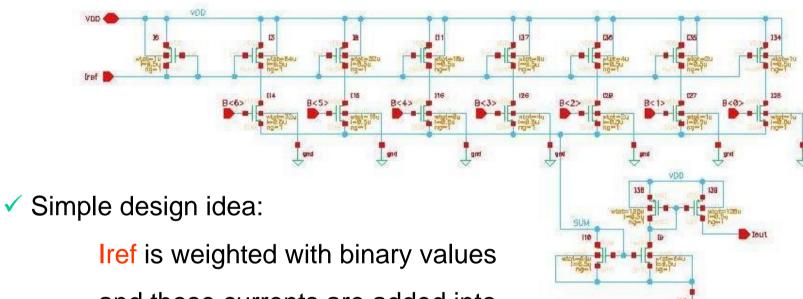

## FIRST 7 BIT DAC DESIGN

and those currents are added into the **SUM** node if the corresponding

B<i> is active

✓ Layout care for maintain linearity

## SIZE, CONDITIONS AND COSTS

- ✓ Expected pin count: ≈ 80 pins

- ✓ Expected area:  $\approx 3 \times 3$  mm<sup>2</sup> (pad limited)

- Deadline for MPW submission: 6 June 2001

- Delivery of 10 untested prototypes after 13 weeks

- ✓ Silicon cost: 590 Euro/mm<sup>2</sup>, minimum 12 mm<sup>2</sup>  $\Rightarrow$  ≈ 7100 Euro

- ✓ Package cost (84 pin JLCC): 56 Euro × 10 = 560 Euro

- ✓ Total cost: ≈ 7700 Euro

#### PLANNI NG

- ✓ Schematics ready by 15 March

- ✓ Layout of single cells ready by 30 April

- ✓ Full layout ready by 15 May

- ✓ DRC, LVS and backannotation by 20 May

- ✓ GDS II files ready by 6 June

- □ DEADLINE

- Design and fabrication of chip test board in June and July

- Chips back to Genova by 10 September

- ✓ First chip turned on by 11 September.

## OPEN QUESTIONS

- ✓ Electronics working conditions: temperature range?

- ✓ Power budget for the front end: still 1 mW/ch?