# CMS Tracker Synchronization

K. Gill CERN EP/CME

B. Trocme, L. Mirabito Institut de Physique Nucleaire de Lyon

#### **Outline**

- Timing issues in CMS Tracker

- Synchronization method

- Relative synchronization

- Synchronization of readout chain across all channels in system

- Absolute synchronization

- Synchronization with LHC collisions and rest of CMS.

- Monitoring synchronization

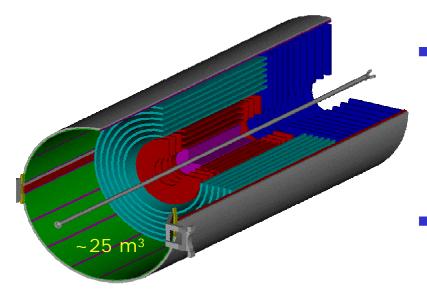

### CMS Silicon Strip Tracker

- Unprecedented use of microstrip technology. Enormous system.

- 210m<sup>2</sup> silicon

- 10 million channels

- Must be very well synchronized to be able to detect, reconstruct and measure particle tracks with expected precision

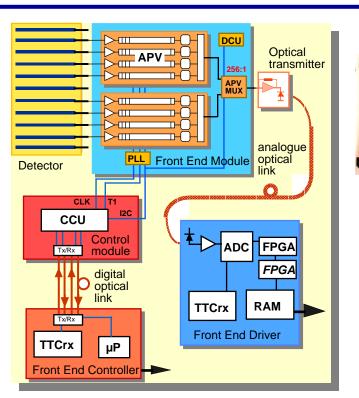

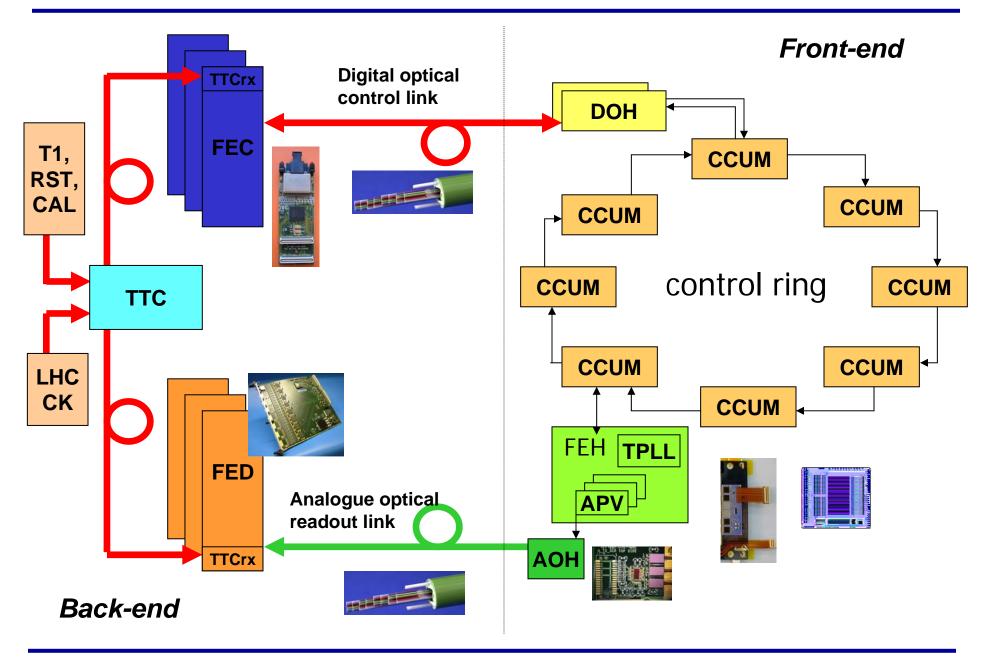

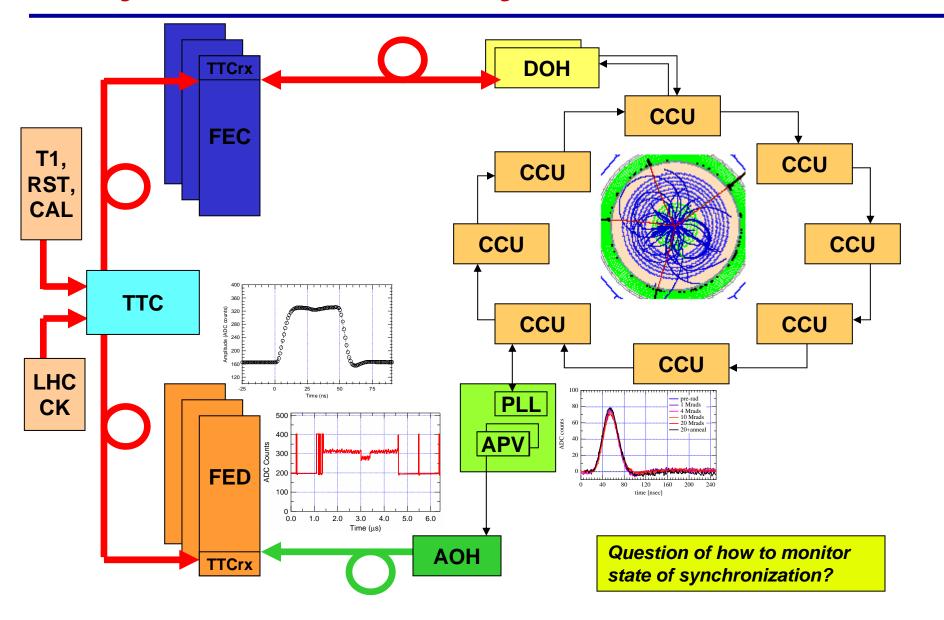

### CMS Tracker readout and control parts

440 FEDs

Starting to look in detail at final system aspects

All parts now defined and in production

Not only large amount of silicon. Rest of system

calibration and synchronization

also large and complex.

320 mFECs

### timing issues: components

### timing issues: cable delays (rough estimates)

#### Tracker timing issues - front-end APVs

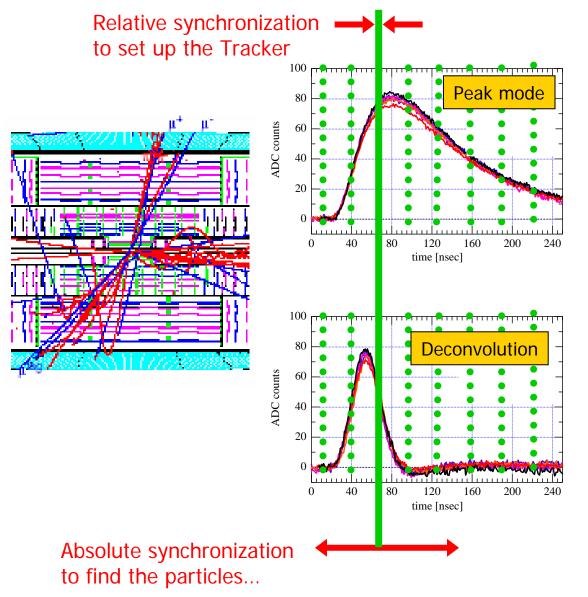

Goal is to synchronize <u>all</u> APVs in Tracker relative to LHC collisions

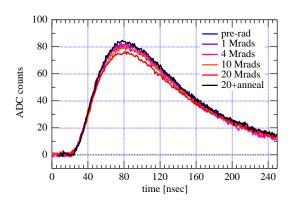

#### (a) APV output in 'peak' mode

Signal is broad, synchronization to ~25ns OK

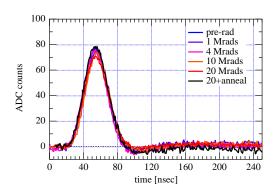

#### (b) 'deconvolution' mode at high luminosity

Peak now narrow, require few ns synchr.

( Also, APV latency must be set correctly to read data from correct pipeline location)

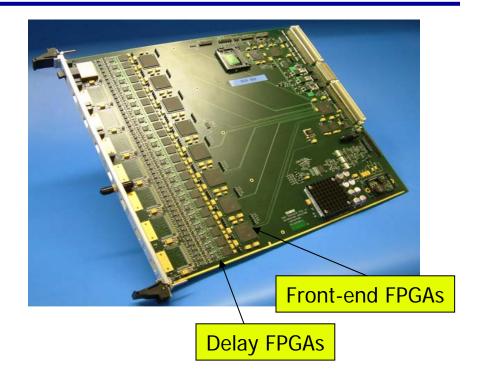

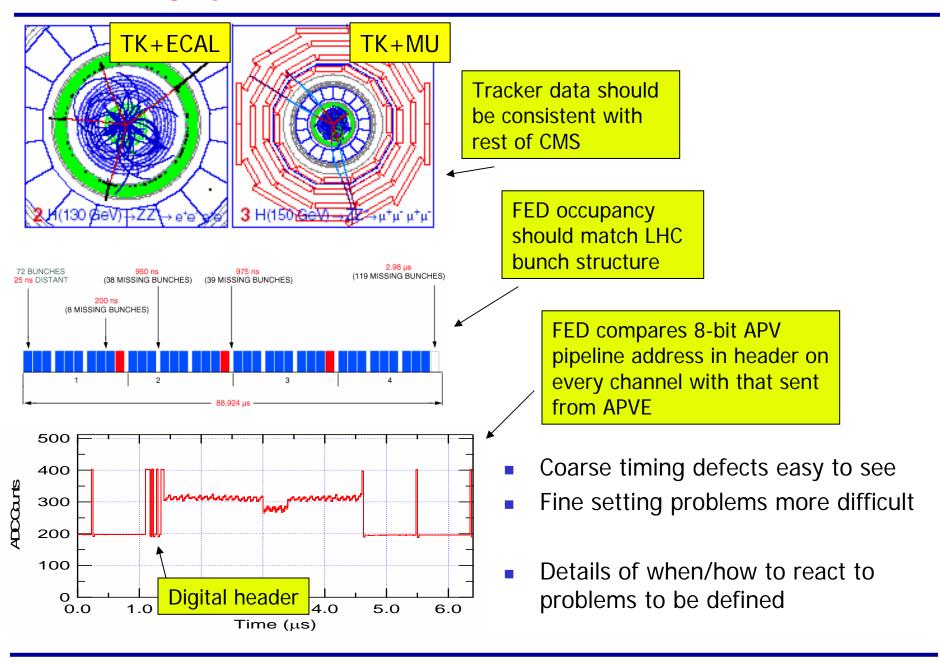

# Timing issues: back-end (FEDs)

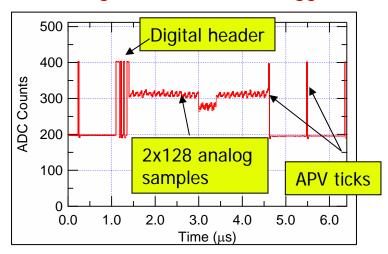

#### (a) APV signals at FED after trigger

FEDs must also be well synchronized

Delay FPGA before front-end FPGA

- Coarse clock skew (25ns steps)

- to analyse same APV sample across whole set of 12 inputs

- Fine clock skew (1ns steps)

- to allow enough settling time (readout b/w<100MHz)</li>

- Need to set to be ~20ns after start of signal pulse

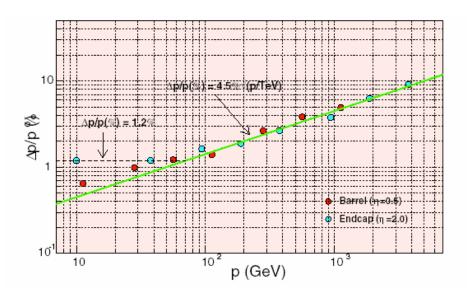

# CMS Tracker synch requirements summary

| Synchronization requirement       | Low luminosity running        | High luminosity running       |

|-----------------------------------|-------------------------------|-------------------------------|

| APV trigger latency setting       | Correct bunch crossing (25ns) | Correct bunch crossing (25ns) |

| APV frame finding at back-end FED | Same clock cycle<br>(25ns)    | Same clock cycle<br>(25ns)    |

| APV sampling of detector signals  | Coarse (25ns)<br>(peak mode)  | Fine (3ns)<br>(deconvolution) |

| Optical link sampling at FED      | Fine (3ns)                    | Fine (3ns)                    |

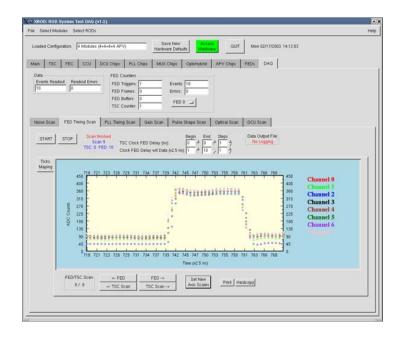

#### Tracker relative synchronization procedure

- Method proposed after experience in 25ns test-beam in 2000

- Based on measurement of time of arrival of APV ticks at FED

- Idea now well thought-out

- Procedure implemented in basic form using XDAQ

- Tested in recent beam/system-tests

- >1 control ring

- >1 prototype FED

- Standalone operation for procedure envisaged in final system

- Local trigger

- Local DAQ FED spy channel/VME

- Idea is that this functionality is available during integration/commissioning

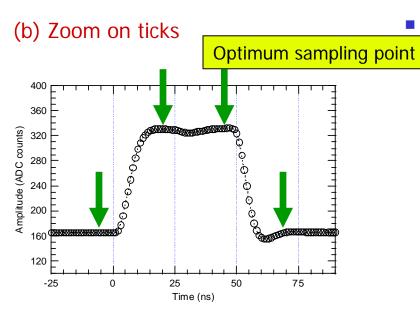

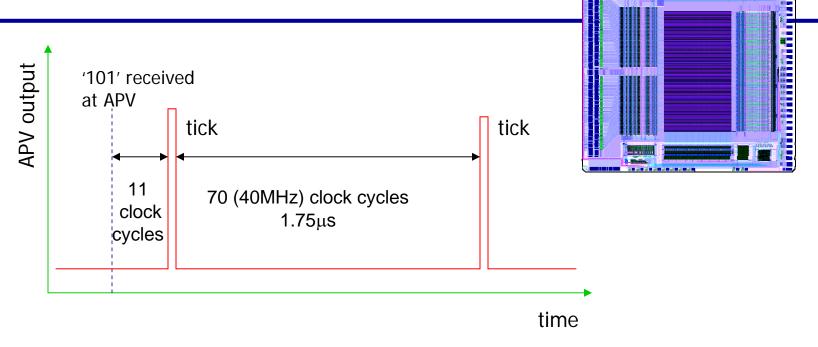

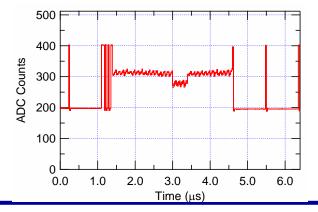

#### APV 'tick-marks'

- APVs 'tick' every 70 clock cycles

- starting at a fixed time after 're-synch' (101) signal received at APV

- Tick transmitted over analogue optical link to FED

- Measure arrival time at FED

(trigger with APV frame OFF)

Knowing analogue optical link lengths

(from database)

- know time when the ticks left the APVs

- therefore use ticks for precise probe of timing skew between APVs

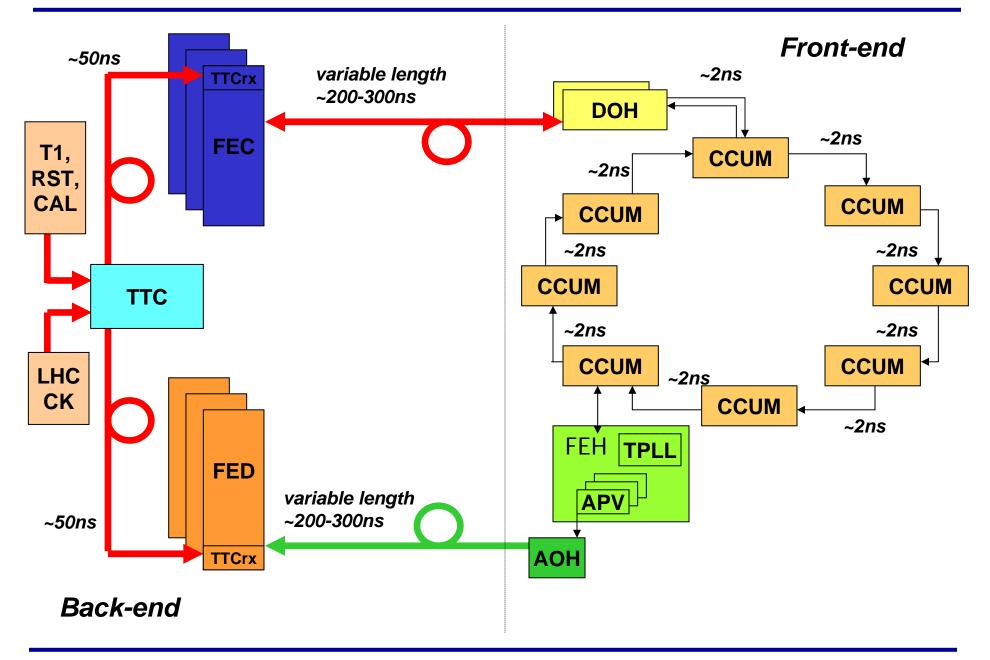

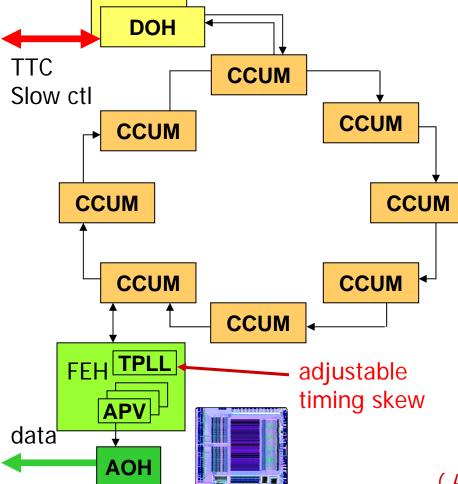

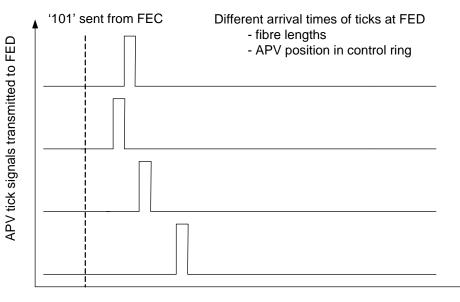

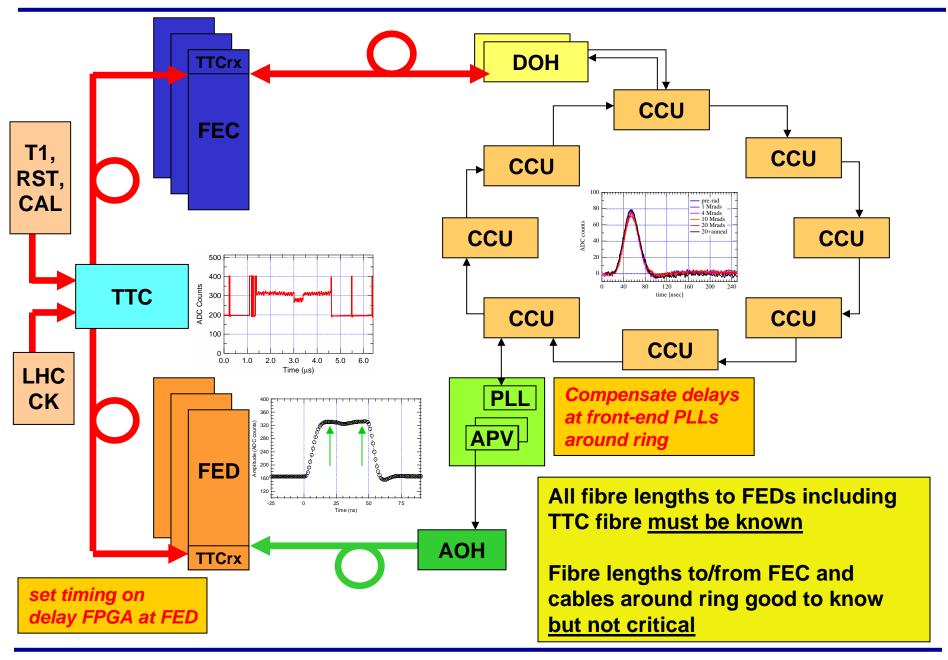

### TK front-end relative synchronization

- At level of 1 control ring/FED relative delays due to

- position of APV around the control ring

- analogue link fibre length

- Build up detailed picture of ticks by sweeping front-end TPLL delay at front-end in 1ns steps

- Knowing analogue fibre lengths then synchronize APVs using the programmable skew on TPLL

- XDAQ implementation for beam and system tests

- L. Mirabito, B. Trocme

- previously N. Marinelli

Time

- Expand method to cover different control rings in partition by comparing signals on different FEDs

- Only ~1 channel/FED needed since inside rings, all APVs already synchronized

- Length of TTC cables to FED must also be known!

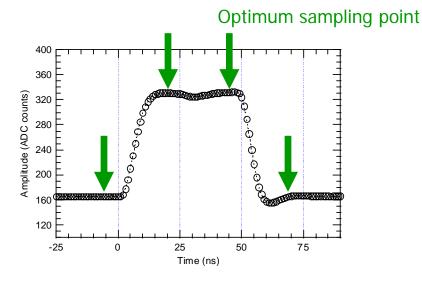

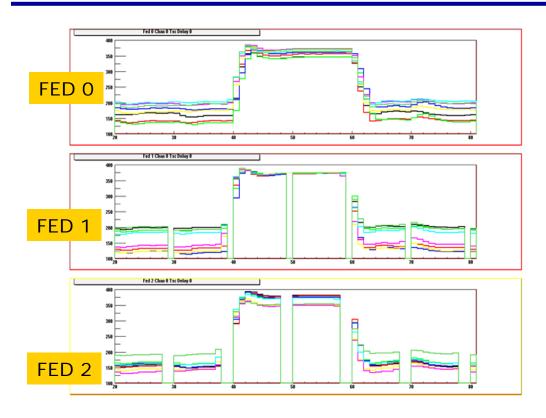

# TK back-end (FED) synchronization - 1

#### (a) APV signals at FED

- Can use APV ticks also to set-up delay FPGAs to synchronize FEDs

- Fine skew setting optimizes analogue signal settling & S/N

- Coarse skew setting signals from same APV pipeline locations processed

- e.g. pedestal subtraction.....

- Do at same time as synchronizing front-end APVs using ticks

### TK back-end (FED) synchronization - 2

- e.g. CMS/TOB tests at CERN

- J. Valls et al, this workshop

Alignment of ticks at FED ensures that APV analogue signals aligned in time for the FED front-end FPGA

### TK relative synchronization summary

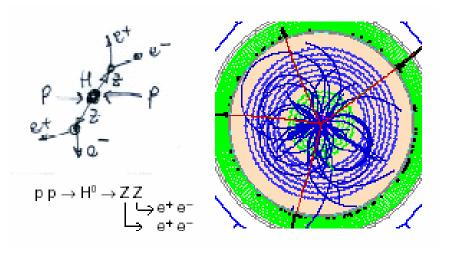

#### Absolute synchronization of CMS Tracker

- Relative synch aligns APVs with respect to one another

- but not to LHC collisions

- or rest of CMS

- Need to align APV sampling to signal generated in silicon strips by passing particles

- Coarse timing

- adjust latency at APV

- Fine timing

- re-adjust PLLs at frontend

- Same procedure as used in beam-tests.

- requires:

- Simple tracking

- Global TRIDAS

### TK synchronization summary

# Checking synchronization

karl.gill@cern.ch

LECC 2003

CMS Tracker Synchronization

#### **Conclusions**

- Timing issues in CMS Tracker well understood

- confident of ability to synchronize final components and whole system

- Could be ready and debugged in advance of LHC collisions

- Relative synchronization procedure based on use of APV tick-marks

- simple, robust, minimal requirements

- Already integral part of start-up procedure for analogue readout system

- Implemented in XDAQ, and tested at level of >1 FEDs/FECs

- system hardware specs/requirements had synch. procedure in mind

- e.g. Optical link fibre lengths

- e.g. FED timing skew provision, scope mode and spy channel

- Absolute synchronization then done by setting correct latency at APV and adjusting PLL fine delays for maximum S/N

- as in beam tests

- Can monitor APVs and FEDs for losses of synchronization during running

- Next steps: further testing, automation and up-scaling of procedures