# VITA 1.5-1999

# DRAFT STANDARD FOR TRIAL USE APPROVED BY THE VITA STANDARDS ORGANIZATION for **2eSST** (source synchronous transfer)

# Secretariat VITA STANDARDS ORGANIZATION

Draft 2.1 Published: December 1, 1999

Publication of this draft standard for trial use and comment has been approved by the VITA Standards Organization. Distribution of this draft standard for comment shall not continue beyond 30 months from the date of publication. It is expected that following this 30 month period, this draft standard, revised as necessary, will be submitted to the American National Standards Institute for approval as an American National Standard. Suggestions for revision should be directed to Mac Rush, Motorola, rush@phx.mcd.mot.com with copy to John Rynearson, VITA, techdir@vita.com.

Compliance to this <u>Draft Standard for Trial Use</u> may be claimed as long as the draft revision is specified. Manufacturers and users are advised that changes are possible before submission for ANSI approval.

VITA Standards Organization 7825 East Gelding Drive, Suite 104 Scottsdale, AZ 85260 Phone: (480) 951-8866 Fax: (480) 951-0720 URL: http://www.vita.com

# **Table of Contents**

| Chapter 1                                        |      |

|--------------------------------------------------|------|

| Introduction to the 2eSST Standard               |      |

| 1.1 VME Protocol Background                      | 9    |

| 1.2 Objectives of the 2eSST Protocol             | 9    |

| 1.3 References                                   | 10   |

| 1.4 Standard Terminology                         | 10   |

| 1.5 Terminology                                  | 11   |

| Chapter 2                                        |      |

| 2eSST Protocol                                   | 13   |

| 2.1 Introduction                                 | 13   |

| 2.2 3U and 6U Implementations.                   | . 13 |

| 2.3 Broadcast Transfers                          | . 13 |

| 2.4 Remapping the LWORD* Line                    |      |

| 2.5 Source Synchronous Transfer                  |      |

| 2.6 Address Phase                                |      |

| 2.6.1 Extended AM codes                          |      |

| 2.6.2 Address Modes                              |      |

| 2.6.3 Transfer Rates                             |      |

| 2.6.4 Known Length 2eSST Transfers               |      |

| 2.6.5 Geographic Address                         |      |

| 2.6.6 Subunit Number                             |      |

| 2.6.7 Odd Bit                                    |      |

| 2.6.8 Broadcast Transfer Address Phase           |      |

| 2.7 Data Phase                                   |      |

| 2.7.1 Broadcast Transfer Data Phase              |      |

| 2.8 Transfer Termination                         |      |

| 2.9 Slave Error Termination                      |      |

| 2.10 Bus Time Out Timer                          |      |

| Chapter 3                                        |      |

| Requirements                                     |      |

| 3.1 Transceivers, Connectors and Backplanes      |      |

| 3.2 Address Phase Protocol                       |      |

| 3.3 Data Phases                                  |      |

| 3.4 Transfer Termination                         |      |

| 3.5 Slave Error Termination                      |      |

| 3.6 Support for Broadcast Transfers              |      |

| 3.7 Bus Time Out Timer                           |      |

| 3.8 Timing Diagrams                              |      |

| Chapter 4                                        |      |

| Theory of Operation                              |      |

| 4.1 Introduction                                 |      |

| 4.2 Source Synchronous Transfers                 |      |

| 4.3 Data Centered Strobes                        |      |

| 4.5 Data Centered Strobes                        |      |

| 4.4 Skew                                         |      |

| 4.4.1 Source skew<br>4.4.2 Backplane Skew        |      |

| 4.4.2 Backplane Skew                             |      |

| 4.4.5 Destination Skew                           |      |

|                                                  |      |

| Appendix A<br>Glossary of Additional 2eSST Terms |      |

| GIOSSALY OF AUDITIONAL 2000 FLEMMS               | ยา   |

# List of Figures

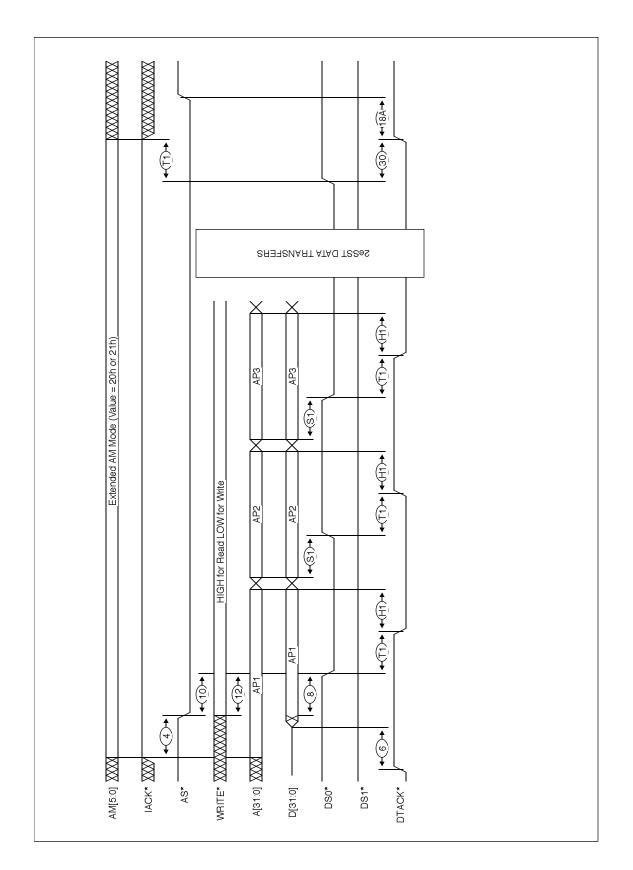

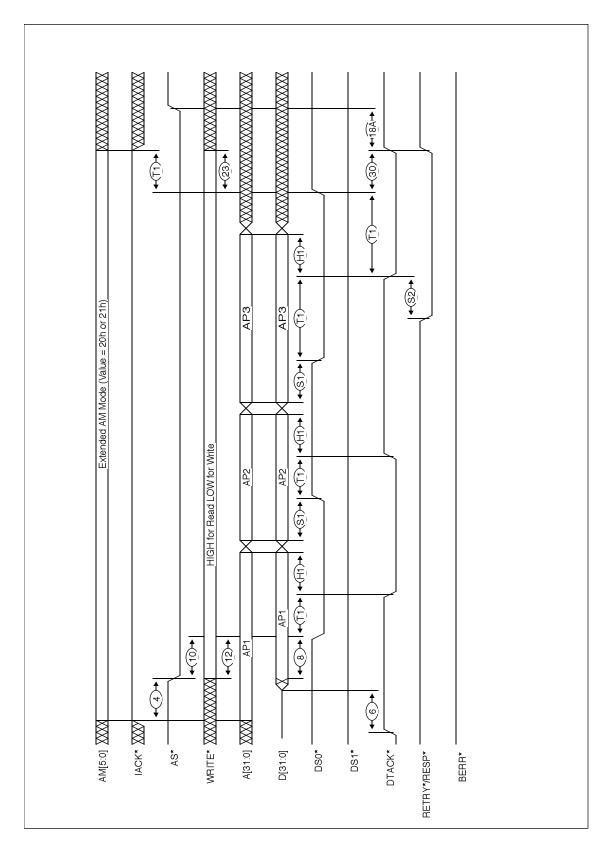

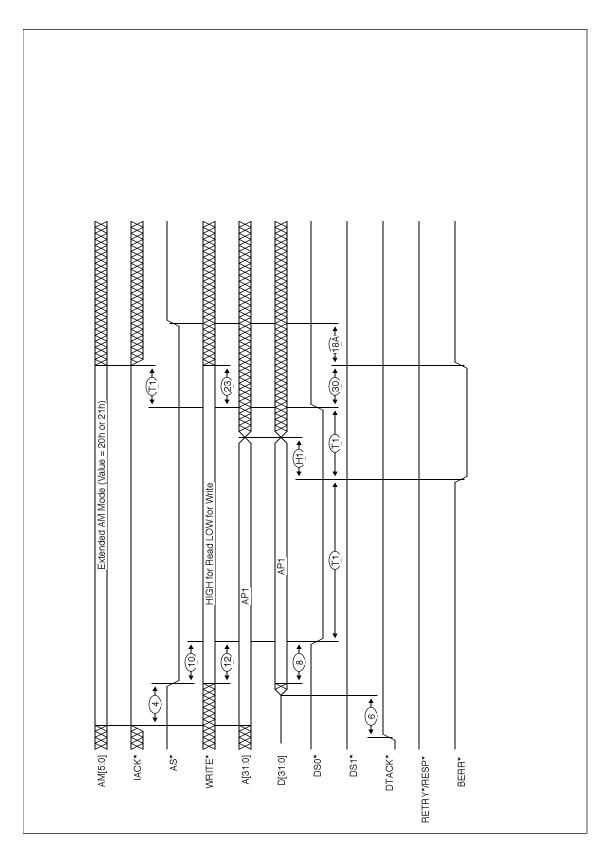

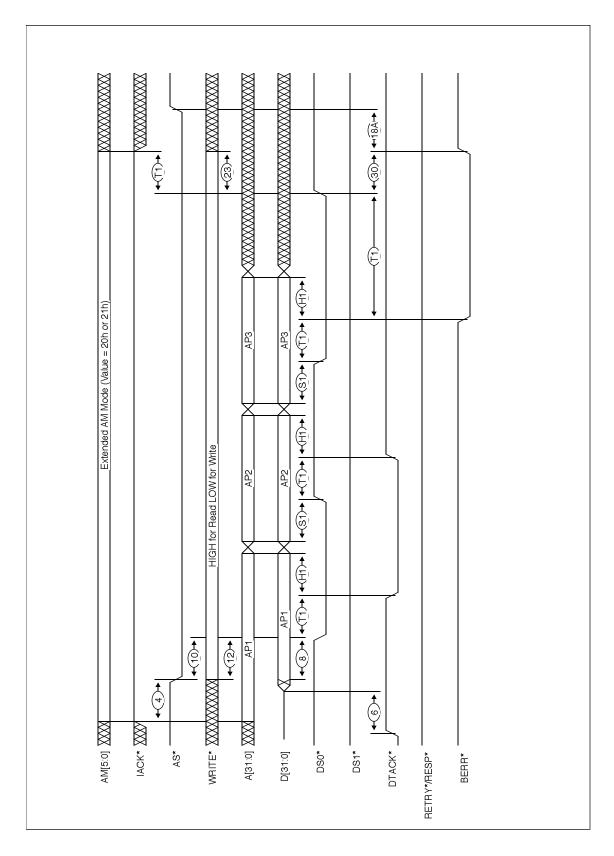

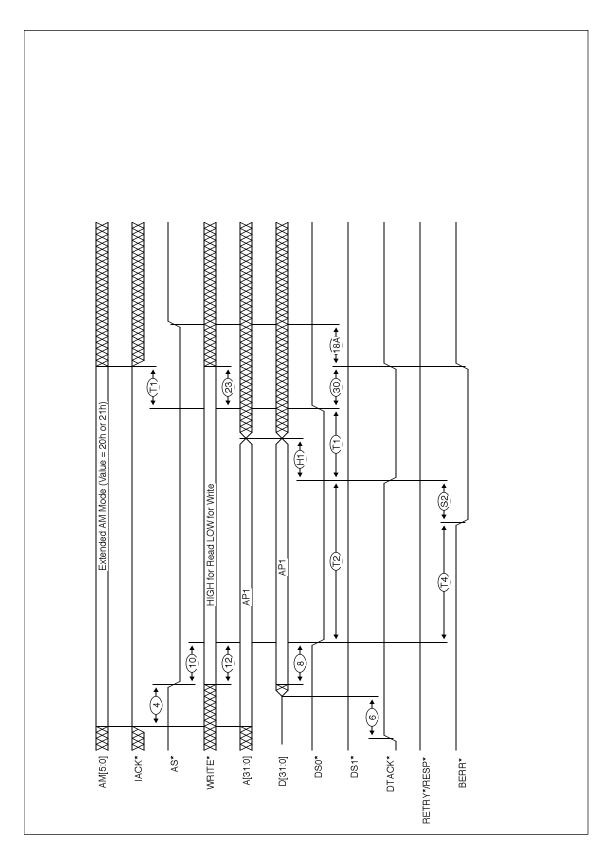

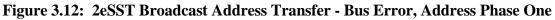

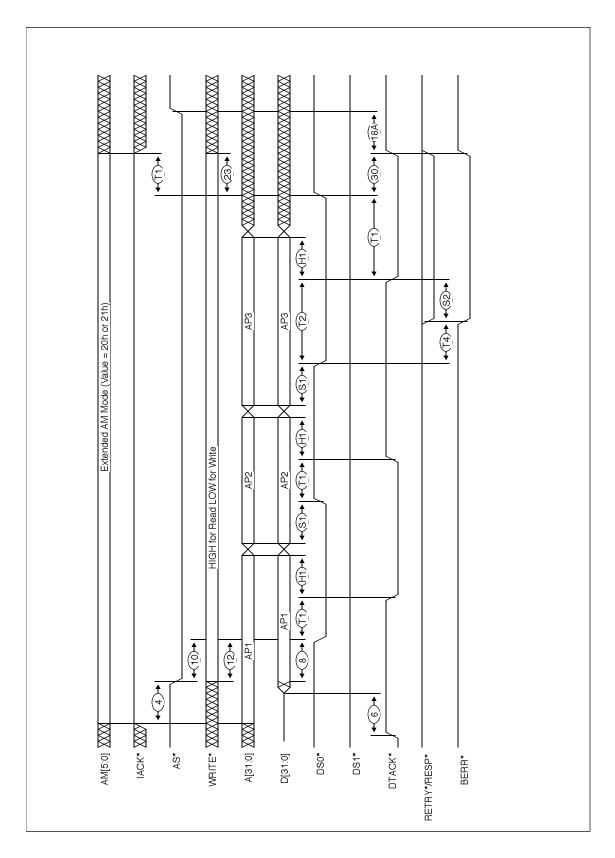

| Figure 3.2: 2eSST Address Transfer - Slave Suspend Response.32Figure 3.3: 2eSST Address Transfer - Bus Error, Address Phase One.33Figure 3.4: 2eSST Address Transfer - Bus Error, Address Phase Three.34Figure 3.5: 2eSST Write.35Figure 3.6: 2eSST Read36Figure 3.7: 2eSST Read, Last Word Invalid.37Figure 3.8: 2eSST Read, Error Termination38Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination.39Figure 3.10: 2eSST Broadcast Address Transfer.40Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response.41Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One.42Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three.43 | Figure 3.1: 2eSST Address Transfer                                             | 31 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----|

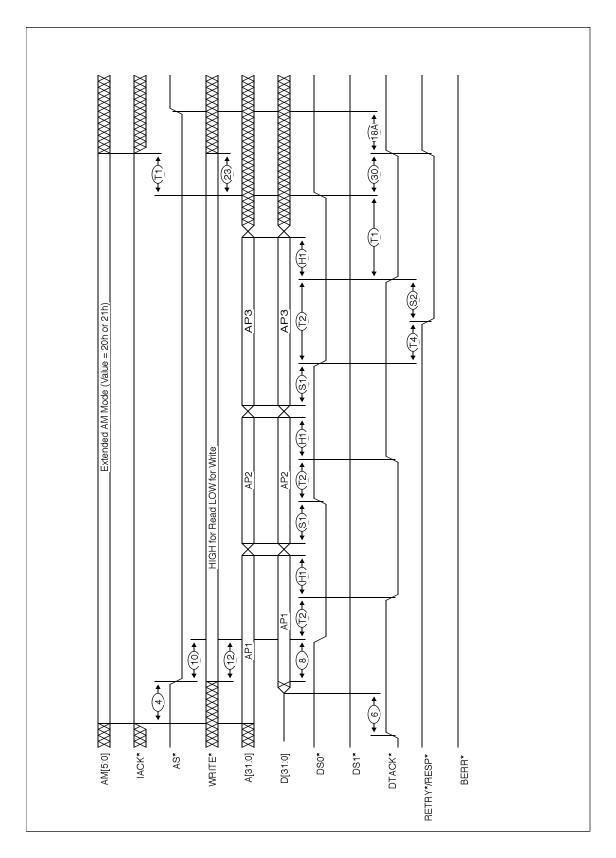

| Figure 3.4: 2eSST Address Transfer - Bus Error, Address Phase Three.34Figure 3.5: 2eSST Write.35Figure 3.6: 2eSST Read36Figure 3.7: 2eSST Read, Last Word Invalid.37Figure 3.8: 2eSST Read, Error Termination38Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination.39Figure 3.10: 2eSST Broadcast Address Transfer.40Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response.41Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One.42Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three.43                                                                                                                                   | Figure 3.2: 2eSST Address Transfer - Slave Suspend Response                    | 32 |

| Figure 3.5: 2eSST Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 3.3: 2eSST Address Transfer - Bus Error, Address Phase One              | 33 |

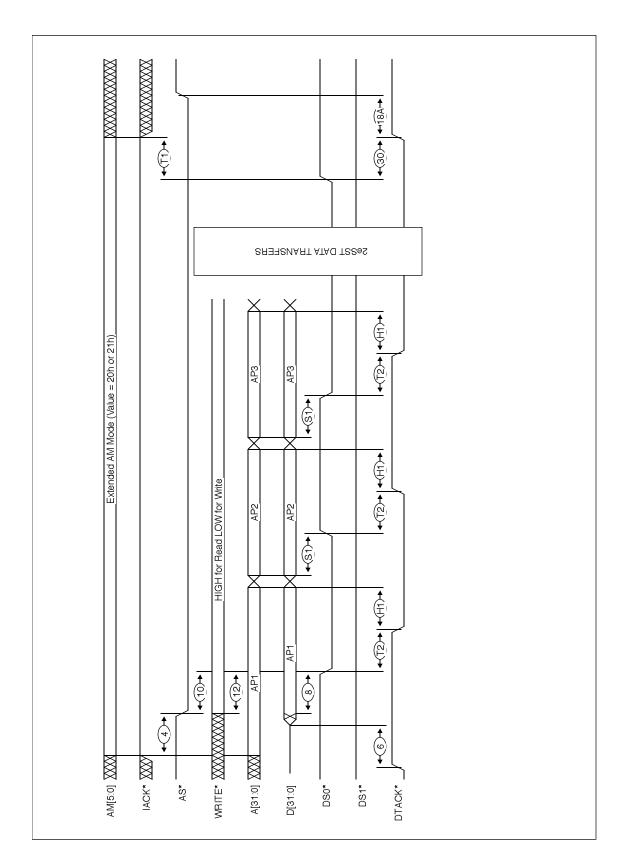

| Figure 3.6: 2eSST Read       36         Figure 3.7: 2eSST Read, Last Word Invalid.       37         Figure 3.8: 2eSST Read, Error Termination       38         Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination.       39         Figure 3.10: 2eSST Broadcast Address Transfer.       40         Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response.       41         Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One.       42         Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three.       43                                                                                                            | Figure 3.4: 2eSST Address Transfer - Bus Error, Address Phase Three            | 34 |

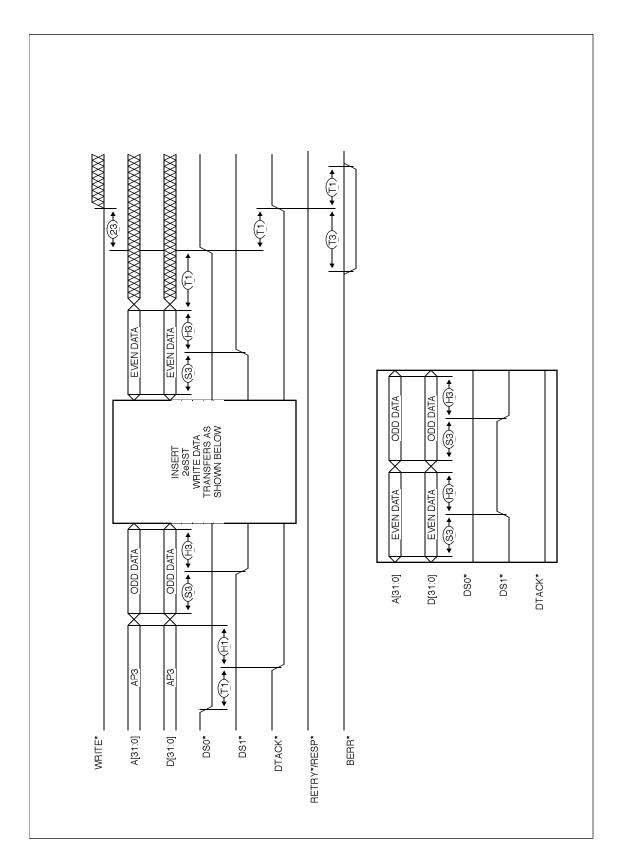

| Figure 3.7: 2eSST Read, Last Word Invalid.       37         Figure 3.8: 2eSST Read, Error Termination       38         Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination.       39         Figure 3.10: 2eSST Broadcast Address Transfer.       40         Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response.       41         Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One.       42         Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three.       43                                                                                                                                                    | Figure 3.5: 2eSST Write                                                        | 35 |

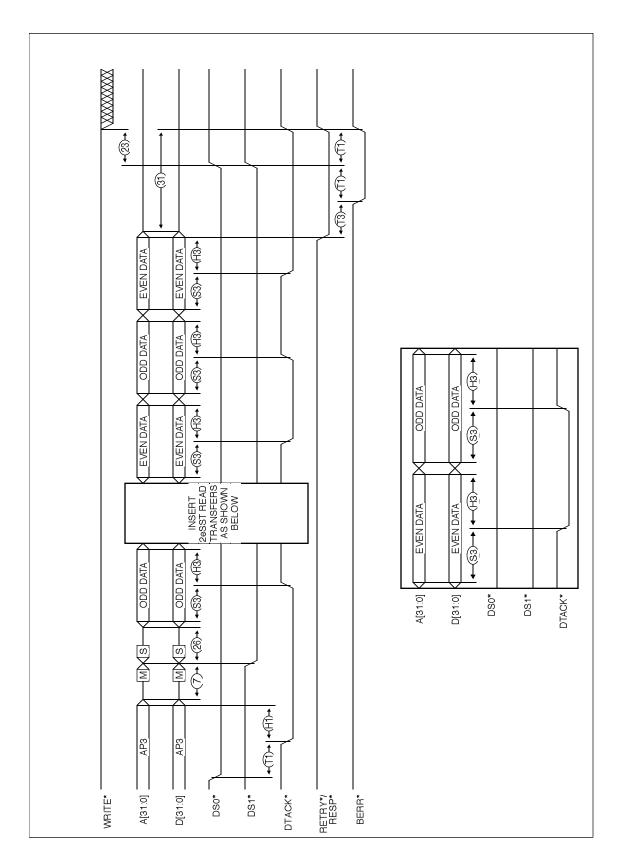

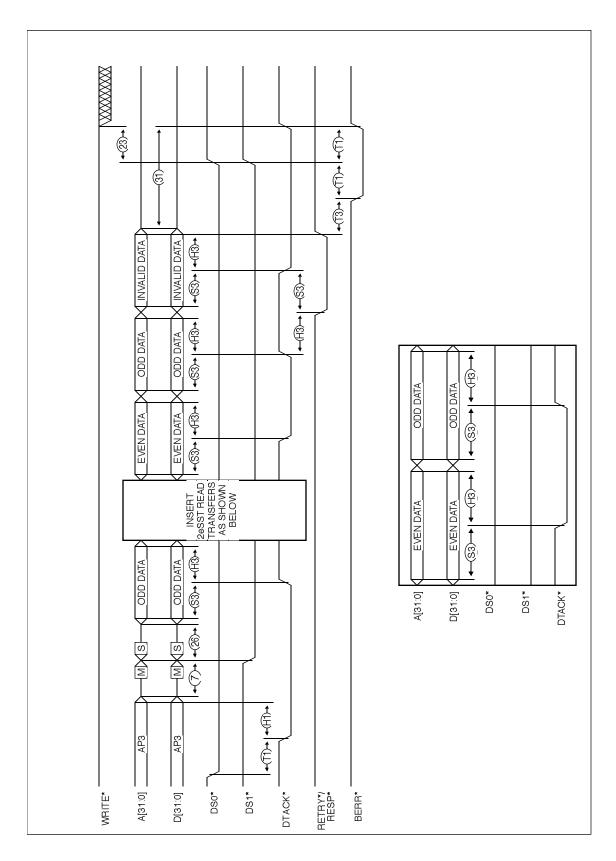

| Figure 3.8: 2eSST Read, Error Termination       38         Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination       39         Figure 3.10: 2eSST Broadcast Address Transfer       40         Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response       41         Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One       42         Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three       43                                                                                                                                                                                                                     | Figure 3.6: 2eSST Read                                                         | 36 |

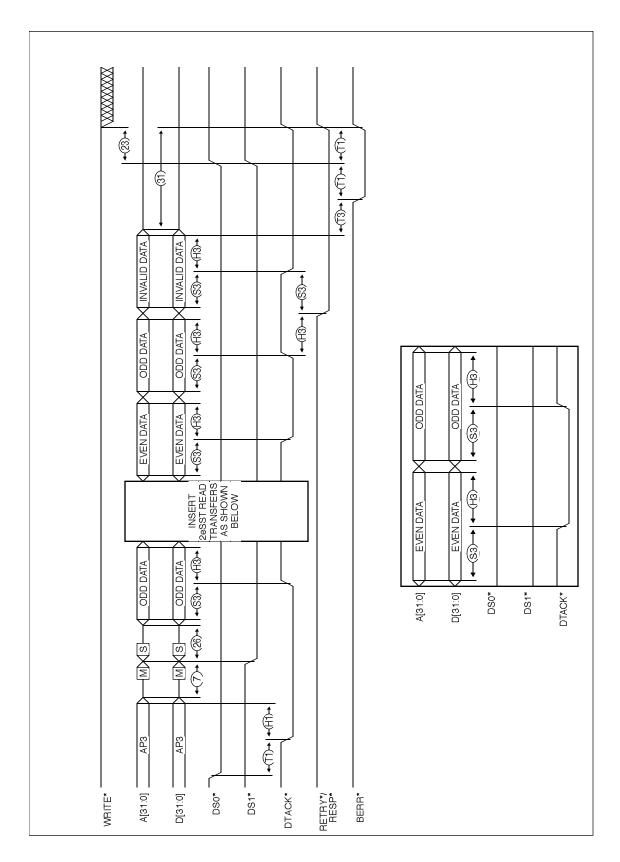

| Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 3.7: 2eSST Read, Last Word Invalid                                      | 37 |

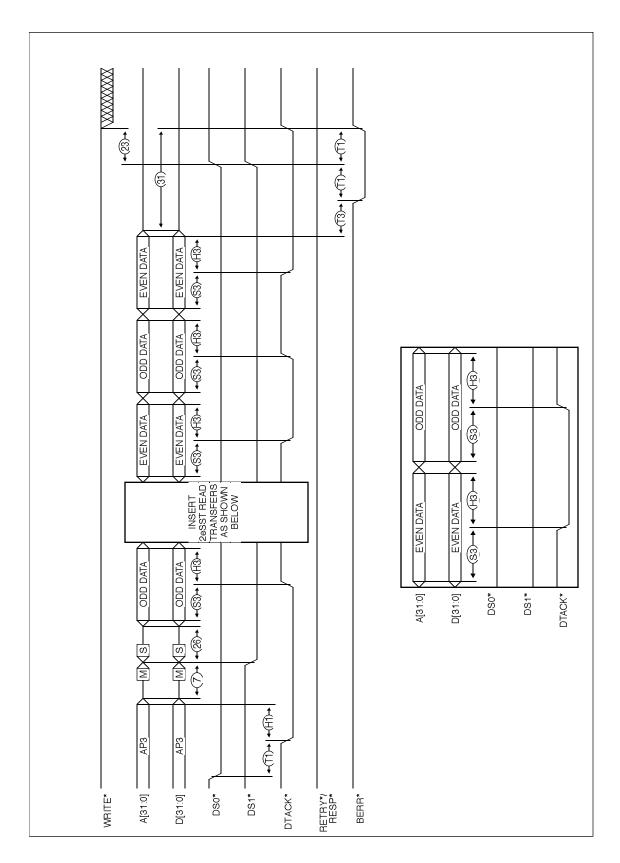

| Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 3.8: 2eSST Read, Error Termination                                      | 38 |

| Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 3.9: 2eSST Read, Last Word Invalid, Error Termination                   | 39 |

| Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 3.10: 2eSST Broadcast Address Transfer                                  | 40 |

| Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 3.11: 2eSST Broadcast Address Transfer - Slave Suspend Response         | 41 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 3.12: 2eSST Broadcast Address Transfer - Bus Error, Address Phase One   | 42 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 3.13: 2eSST Broadcast Address Transfer - Bus Error, Address Phase Three | 43 |

| Figure 3.14: 2eSST Broadcast Write 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 3.14: 2eSST Broadcast Write                                             | 44 |

| Figure 2.15: 2088T Strobe Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 3.15: 2eSST Strobe Timing                                               | 45 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |    |

# List of Tables

| 0  |

|----|

| 4  |

| 5  |

| 5  |

| 6  |

| 7  |

| 7  |

| 29 |

| 80 |

| 80 |

| 50 |

|    |

## Abstract

This draft standard is an extension to the VME64 (ANSI/VITA 1-1994) and VME64x (VITA1.1-1997) standards. It defines a new transfer protocol, based upon source synchronous concepts, that permits the VMEbus to operate at rates up to 320MB/s. As technology improves, this rate may be extend to higher levels.

## Foreword

Since the VMEbus was developed in the early 80's, it has been continuously enhanced. New features have been added and new technologies have been adopted to increase the utility and performance. This standard adds a new protocol to further enhance the performance of the VMEbus.

## Preface

The 2eSST protocol requires low skew between signals and monotonic rising and falling edges on the signals. To meet these requirements, limited length backplanes, special backplane topologies and/or enhanced transceivers are required. At the present time, a family of bus transceivers with the enhanced characteristics are not available. The enhanced bus transceivers should have controlled rise and fall times, tightly defined thresholds, low part to part skew and LVTTL levels. Most standard TTL bus transceivers do not have tightly specified thresholds, skew specifications or rise and fall time specifications. The family of drivers should include a variety of standard parts for use with various implementations. For the data and address signals, 245 style transceivers and transceivers and 646 style transceivers with latches should be available. For the strobes and acknowledge signals, 125 style drivers with individual enables should be available. The drivers should also have LVTTL levels for use with sub-micron semiconductor technologies. The 2eSST draft standard is being approved for trial use to allow the driver and backplane technologies to develop.

## **Comments, Corrections, Additions**

This document was started by Drew Berding, Arizona Digital, and Jonathan Morris, Tundra Semiconductor, and is currently being edited by Mac Rush, Motorola. At the present time, all comments, corrections or additions should be addressed to:

Mac Rush Document Editor Motorola Computer Group 2900 S. Diablo Way M.D. DW278 Tempe, AZ 85282 Phone: 602-438-3019 Fax: 602-438-3836 Email: rush@phx.mcd.mot.com

# **Draft History**

| Draft<br>Number | Date               | Changes/Comments                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D1.0            | June 6, 1997       | First draft                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| D1.1            | June 30, 1997      | Total revision of Chapter 5; Remove Trademarks; addition of section 3.1.3                                                                                                                                                                                                                                                                                                                                                         |  |

| D1.2            | June 30,1997       | Re-organized document to mimic other VSO documents and expanded text on protocol.                                                                                                                                                                                                                                                                                                                                                 |  |

| D1.3            | January 12, 1998   | Add comments from the July VSO meeting and additional text.                                                                                                                                                                                                                                                                                                                                                                       |  |

| D1.4            | March 17, 1998     | Add comments from January VSO meeting. Converted to FrameMaker. Added section on broadcast and broadcall.                                                                                                                                                                                                                                                                                                                         |  |

| D1.5            | April 20, 1998     | Redefined the fields in address phase two and three.<br>Increased the size of the beat count field and changed the<br>name to cycle count. Removed broadcall. Added a bit to<br>indicate broadcast transfers and added slave select bits for<br>broadcast transfers. Transfer rate is now defined by a trans-<br>fer rate field rather than XAM codes. Simplified protocol by<br>allowing only the source to terminate the cycle. |  |

| D1.6            | July 1, 1998       | Added comments from the first task group ballot and May VSO meeting. Re-numbered rules, observations.                                                                                                                                                                                                                                                                                                                             |  |

| D1.7            | November 3, 1998   | Added comments from the July and September VSO meetings.                                                                                                                                                                                                                                                                                                                                                                          |  |

| D1.8            | June 7, 1999       | Added comments from the second task group ballot, January VSO meeting, March VSO meeting and May VSO meeting.                                                                                                                                                                                                                                                                                                                     |  |

| D1.9            | September 13, 1999 | Added comments from the third task group ballot and July VSO meeting.                                                                                                                                                                                                                                                                                                                                                             |  |

| D2.0            | October 22, 1999   | Added comments from the third task group ballot and September VSO meeting.                                                                                                                                                                                                                                                                                                                                                        |  |

| D2.1            | December 1, 1999   | Added trial use notice and comments from the November VSO meeting.                                                                                                                                                                                                                                                                                                                                                                |  |

# **Task Group Members**

| Name            | Position        | Company                 |

|-----------------|-----------------|-------------------------|

| Mac Rush        | Chairman        | Motorola Computer Group |

| Chau Pham       | Vice Chairman   | Motorola Computer Group |

| Drew Berding    | Document Editor | Arizona Digital         |

| Ed Barsotti     | Member          | Fermilab                |

| Bob Downing     | Member          | VIPA                    |

| Denis Dubois    | Member          | Tundra Semiconductor    |

| Markus Joos     | Member          | CERN                    |

| Tad Kubic       | Member          | Dawn VME Products       |

| Jing Kwok       | Member          | DY 4 Systems            |

| Tony Lavely     | Member          | Mercury Computer        |

| Andreas Lenkish | Member          | Trenew                  |

| Greg Novak      | Member          | Motorola Computer Group |

| Elwood Parsons  | Member          | AMP                     |

| John Rynearson  | Member          | VITA                    |

| Ron Seese       | Member          | Chrislin                |

| Robert Sullivan | Member          | Hybricon                |

| Mark Taylor     | Member          | Bechtel Bettis          |

| Larry Thompson  | Member          | Navel Surface Warfare   |

| Istvan Vadasz   | Member          | Force Computers         |

The 2eSST Task Group consists of the following members:

# **Chapter 1**

# Introduction to the 2eSST Standard

# **1.1 VME Protocol Background**

There have been several types of cycles defined throughout the history of the VMEbus standards:

SCT: Single Cycle Transfer is the traditional VMEbus read or write cycle. During a single cycle transfer, only a single data transfer of up to 32 data bits (up to four bytes) occurs. Single cycle transfers have a theoretical maximum transfer rate of 40 MB/s.

BLT: During a Block Transfer, the starting address is transferred followed by multiple data transfers. The master and slave increment their address counters with each data transfer. This allows faster operation than multiple single cycles for certain kinds of slaves (such as DRAM memory boards) since only the initial address has to be transferred. Block transfers also allow more efficient use of write post and read ahead buffers because the data is sequential. BLT transfers have a theoretical maximum transfer rate of 40 MB/s.

MBLT: Multiplexed BLock Transfer is defined in the VME64 standard. MBLT utilizes the 32 data lines plus the 31 address lines and LWORD\* as a single 64-bit bus. This bus is time multiplexed between address and data, and after the address transfer, the entire bus is used for multiple data transfers. MBLT allows twice the transfer rate of BLT since it has twice the number of data bits. MBLT transfers have a theoretical maximum transfer rate of 80 MB/s.

2eVME: Two edge VME is defined by the VME64x standard. The 2eVME protocol utilizes both edges of the control signals to transfer data. Since both edges of the control signals are used, only one round trip bus delay is encountered instead of the two round trip bus delays that are encountered when the SCT, BLT and MBLT protocols are used. 2eVME transfers have a theoretical maximum transfer rate of 160 MB/s.

2eSST: Two edge Source Synchronous Transfer is the subject of this standard. As a source synchronous protocol, the performance of 2eSST is determined not by the propagation delay from source to destination, but by skew --- the variation in propagation delay through the drivers, backplane and receivers. As the skew decreases, the bandwidth of the system can increase. In theory, as technology improves, a source synchronous protocol is virtually unlimited in its potential transfer rate. This standard provides for transfer rates of 160, 267 and 320 MB/s with a 21 slot backplane. New transfer rates can be defined as the technology improves.

# **1.2 Objectives of the 2eSST Protocol**

In developing the 2eSST protocol, several important objectives were considered:

Maximize Performance: Performance was the driving impetus for this new protocol. To meet this objective, the protocol was designed to ensure that all devices involved in the transfer would operate as fast as possible. For example, the protocol does not permit throttling, implying that the receiver of a transaction must be able to operate at the requested speed.

Minimize Complexity: The 2eSST protocol was designed to minimize the amount of logic that would be required to implement the protocol. This was made in light of the fact that most 2eSST interfaces would also support traditional VME protocols and the 2eVME protocol.

Minimize Application Limits: The 2eSST protocol can be used in 3U, 6U and 9U environments, using the new 160-pin connector defined in the VME64x standard.

**Draft Standard for Trial Use**

Maintain Compatibility: The 2eSST protocol and the previous 2eVME protocol and MBLT protocol were designed to be compatible with legacy VMEbus products. However, at the highest transfer rate defined by the 2eSST protocol, the DS1\* and DTACK\* signals will have pulse widths narrower than defined by the VME64 standard or VME64x standard. This is not a problem since legacy boards will not be participating in 2eSST transactions.

# **1.3 References**

The following publications are used in conjunction with this standard. When they are superseded by an approved revision, that revision must apply.

| Document           | Description                                                              |  |  |

|--------------------|--------------------------------------------------------------------------|--|--|

| ANSI/VITA 1-1994   | VME64 Standard, Approved April 10, 1995                                  |  |  |

| ANSI/VITA 1.1-1997 | VME64x Standard, Approved October 7, 1998                                |  |  |

| VITA 2-199x        | Enhanced Transceiver Logic                                               |  |  |

| IEC 61076-4-113    | 2.54 mm 160 pin connectors complementary to IEC 603-2 Style C connectors |  |  |

Table 1.1: References

# **1.4 Standard Terminology**

To avoid confusion and to make very clear what the requirements for compliance are, many of the paragraphs in this standard are labeled with keywords that indicate the type of information they contain. The keywords are listed below:

Rule Recommendation Suggestion Permission Observation

These key words are used as follows:

# Rule <chapter>.<number>:

Rules form the basic framework of this draft standard. They are sometimes expressed in text form and sometimes in the form of figures, tables or drawings. All rules shall be followed to ensure compatibility between board and backplane designs. All rules use the "SHALL" or "SHALL NOT" words to emphasize the importance of the rule. The upper-case "SHALL" or "SHALL NOT" words are reserved exclusively for stating rules in this standard and are not used for any other purpose.

## **Recommendation <chapter>.<number>:**

Wherever a recommendation appears, designers would be wise to take the advice given. Doing otherwise might result in some awkward problems or poor performance. While the 2eSST architecture has been designed to support high-performance systems, it is possible to design a system that complies with all the rules but has poor performance. In many cases a designer needs a certain level of experience in order to design boards that deliver top performance. Recommendations found in this standard are based on this kind of experience and are provided to designers to speed their traversal of the learning curve. All recommendations use the "SHOULD" or "SHOULD NOT" words to emphasize the importance of the recommendation. The upper-case "SHOULD" or "SHOULD NOT" words are reserved exclusively for stating recommendations in this draft standard and are not used for any other purpose.

10

#### Suggestion <chapter>.<number>:

A suggestion contains advice that is helpful but not vital. The reader is encouraged to consider the advice before discarding it. Some design decisions that need to be made in designing boards are difficult until experience has been gained. Suggestions are included to help a designer who has not yet gained this experience. Some suggestions have to do with designing boards that can be easily reconfigured for compatibility with other boards, or with designing the board to make the job of system debugging easier.

#### **Permission <chapter>.<number>:**

In some cases a rule does not specifically prohibit a certain design approach, but the reader might be left wondering whether that approach might violate the spirit of the rule or whether it might lead to some subtle problem. Permissions reassure the reader that a certain approach is acceptable and will cause no problems. All permissions use the "**MAY**" words to emphasize the importance of the permission. The upper-case word "**MAY**" words are reserved exclusively for stating permissions in this draft standard and are not used for any other purpose.

#### **Observation <chapter>.<number>:**

Observations do not offer any specific advice. They usually follow naturally from what has just been discussed. They spell out the implications of certain rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules so that the reader understands why the rule shall be followed.

## **1.5 Terminology**

In this standard, hexadecimal numbers are preceded by a 0x prefix. For example, the hexadecimal number 20 would be represented as 0x20 in this standard.

In this standard, buses are represented by a bus name followed by a bit field. For example, a bus could be represented as D[31:0] where "D" is the bus name and "[31:0]" represents the bits 31 to 0 inclusive where bit 31 is the most significant bit and 0 is the least significant bit.

In this standard, active low signals are indicated by an "\*" following the signal name.

This page left blank intentionally.

# Chapter 2

# **2eSST Protocol**

# 2.1 Introduction

The 2eSST protocol was designed to enhance the performance of the VMEbus. The 2eSST protocol defines three new transfers rates for the VMEbus that are based on source synchronous transfer technology. The new transfer rates are 160 MB/s, 267 MB/s and 320 MB/s. The 2eSST protocol also provides for broadcast data transfers. A broadcast data transfer allows the master to transfer the same data to multiple slaves with a single transfer.

# 2.2 3U and 6U Implementations

The VMEbus standards define several different VME board sizes: 3U, 6U and 9U. The 2eSST protocol, like the previous VMEbus protocols, was designed to support the various board sizes. 3U boards only connect to the VMEbus through the P1 connector and the signals on the P2 connector are not available. 3U boards have a 32-bit data bus, a 32-bit or 40-bit address bus and they use the RESP\* signal. 3U boards use the 3U implementation of the 2eSST protocol.

6U and 9U VME boards generally connect to the VMEbus using the P1 and P2 connectors. Boards that connect to the VMEbus using the P1 and P2 connectors are considered 6U boards. Boards that connect to the VMEbus through only the P1 connector are considered 3U boards. 6U boards have a 64-bit data bus, a 32-bit or 64-bit address bus and use the RETRY\* signal. 6U boards use the 6U implementation of the 2eSST protocol.

In this standard, the signal RETRY\*/RESP\* is used to indicate that boards using the 6U implementation will use the RETRY\* signal and boards using the 3U implementing will use the RESP\* signal. A board using the 6U implementation can communicate with a board using the 3U implementing and when it does, it must use the RESP\* signal. If a board using the 6U implementing is to be compatible with both boards using the 3U and 6U implementations, it must be able to monitor and drive both RETRY\* and RESP\* signals. However, a board using the 6U implementation must not connect RESP\* and RETRY\* together since a single driver should not be used to drive two VMEbus traces.

# **2.3 Broadcast Transfers**

The current VMEbus protocols allow a VMEbus master to write data to a specific VMEbus slave. If a master needs to transfer the same data to multiple slaves, the master would send the data to each slave individually. For example, to transfer a block of data to 20 slaves, the master would transfer the same block 20 times. In contrast, the 2eSST protocol supports broadcast transfers which allow a master to write the same data to multiple slaves with a single transfer. Using the broadcast transfer capability of the 2eSTT protocol, the master can transfer a block of data to 20 slaves using a single transfer. Broadcast transfers support one slave per VMEbus slot which allows a maximum of 21 slaves in a 21 slot VMEbus backplane. During a broadcast transfer, all slaves are considered participating slaves rather that responding slaves. A participating slave receives the data but has limited interaction with the master.

# 2.4 Remapping the LWORD\* Line

In the VME64 standard, the 32-bit address bus and the 32-bit data bus are combined to form a 64-bit data bus to provide a path for the 64-bit data transfers. Since the VMEbus lacks an address bit 0, the LWORD\* line is redefined as address bit 0, A[0]. This effectively provides a full 32-bit address bus, labeled A[31:0], and reflects the usage of the line. Therefore, during the data phase, the address lines A[31:1] are used as data lines D[63:33] and the LWORD\* signal A[0] is used as data line D[32] by the MBLT, 2eVME and 2eSST

|--|

protocols.

# 2.5 Source Synchronous Transfer

The main difference between the 2eSST protocol and the 2eVME protocol is that during the 2eSST data phases, the protocol is source synchronous. No acknowledgment is expected from the receiver of the data. Hence, the theoretical performance of 2eSST is limited only by the skew between transmitter and receiver of data. Like the 2eVME protocol, the 2eSST protocol uses both edges of the strobe to transfer data. The result is a protocol that defines a transfer rate of 320 MB/s, which is double the theoretical transfer rate of 2eVME.

The protocol can be broken into three main phases: address phase, data phase and termination phase.

# 2.6 Address Phase

The address phase of the 2eSST protocol is similar to the 2eVME protocol. The 2eSST address phase is split into three phases, address phase one, address phase two and address phase three. Three times as much information can be transferred during a 2eSST address transfer as compared to a VME64 address transfer. Table 2.1 defines the signal fields during the address phase for 6U implementations. Table 2.2 defines the signal fields during the address phase for 3U implementations.

| Signal<br>Line | Address<br>Phase 1                       | Address<br>Phase 2                                             | Address<br>Phase 3                                        | Data<br>Phase |

|----------------|------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------|---------------|

| AM[5:0]        | 0x20                                     | 0x20                                                           | 0x20                                                      | 0x20          |

| A[7:0]         | XAM Code<br>(Table 2.4)                  | A[3:0] = 0<br>Device Address<br>A[7:4]                         | For XAM = 11,12<br>A[23:0] = Reserved                     | D[39:32]      |

| A[15:8]        | Device Address<br>A[15:8]                | Cycle Count                                                    | For XAM = 21,22<br>A[0] = Reserved<br>A[21:1] = Broadcast | D[47:40]      |

| A[23:16]       | Device Address<br>A[23:16]               | A[23:21] = 0<br>A[20:16] = GA of Master                        | Slave Select<br>A[23:22] = Reserved                       | D[55:48]      |

| A[31:24]       | Device Address<br>A[31:24]               | Subunit Number<br>in Master                                    | Reserved                                                  | D[63:56]      |

| D[31:0]        | Device Address<br>A[63:32] (= 0 for A32) | D[3:0] = Transfer Rate<br>D[4] = Odd Bit<br>D[31:5] = Reserved | Reserved                                                  | D[31:0]       |

| Signal<br>Line | Address<br>Phase 1                       | Address<br>Phase 2                                                | Address<br>Phase 3                                         | Data<br>Phase |

|----------------|------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------|---------------|

| AM[5:0]        | 0x21                                     | 0x21                                                              | 0x21                                                       | 0x21          |

| A[7:0]         | XAM Code<br>(Table 2.4)                  | A[3:0] = 0<br>Device Address A[7:4]                               | For XAM = 11,12<br>A[23:0] = Reserved                      | D[23:16]      |

| A[15:8]        | Device Address<br>A[15:8]                | Cycle Count                                                       | For XAM = 21,22<br>A[0] = Reserved                         | D[31:24]      |

| A[23:16]       | Device Address<br>A[23:16]               | A[23:21] = 0<br>A[20:16] = GA of Master                           | A[21:1] = Broadcast<br>Slave Select<br>A[23:22] = Reserved | Reserved      |

| D[7:0]         | Device Address<br>A[31:24]               | Subunit Number<br>in Master                                       | Reserved                                                   | D[7:0]        |

| D[15:8]        | Device Address<br>A[39:32] (= 0 for A32) | D[11:8] = Transfer Rate<br>D[12] = Odd Bit<br>D[15:13] = Reserved | Reserved                                                   | D[15:8]       |

Table 2.2: 3U Address Phase Signal Field Definitions

Normally the address phase is followed by a data phase. However, the slave can terminate the transfer during address phase one or three. There are two ways the slave can terminate the transfer.

During address phase one or three, the slave can respond with a slave error response by asserting BERR\*. During address phase three, the slave can respond with a slave suspend response by asserting RETRY\*/RESP\* and DTACK\*. The master can retry a transfer that is terminated with a slave suspend response.

# 2.6.1 Extended AM codes

Since there are only a few unassigned address modifier codes left, an extended address modifier (XAM) coding scheme is used. AM code 0x20 is assigned for enhanced data transfer protocols on 6U implementations and AM code 0x21 is assigned for enhanced data transfer protocols on 3U implementations. The eight LSB (Least Significant Bits) of the address field A[7:0] are used to carry the XAM code information during the first address phase. See Table 2.3, which maps the address lines to the XAM code field. With 8-bits, 256 additional address modifier codes are available for 6U implementations and 256 additional address modifier codes are available for 3U implementations.

Table 2.3: Extended Address Modifier Line Definitions

| A7   | A6   | A5   | A4   | A3   | A2   | A1   | A0   |

|------|------|------|------|------|------|------|------|

| XAM7 | XAM6 | XAM5 | XAM4 | XAM3 | XAM2 | XAM1 | XAM0 |

The 2eSST definition defines four XAM codes. The XAM code definitions are shown in Table 2.4. With 256 possible XAM codes for each board size, the extended address addition leaves plenty of room for future expansion.

| Address Modifier Code<br>Implementation | Extended Address<br>Modifier Code | Address/Data<br>Mode     |

|-----------------------------------------|-----------------------------------|--------------------------|

|                                         | 0x11                              | A32/D64 2eSST            |

| 0x20                                    | 0x12                              | A64/D64 2eSST            |

| 6U                                      | 0x21                              | A32/D64, Broadcast 2eSST |

|                                         | 0x22                              | A64/D64, Broadcast 2eSST |

|                                         | 0x11                              | A32/D32 2eSST            |

| 0x21<br>3U                              | 0x12                              | A40/D32 2eSST            |

|                                         | 0x21                              | A32/D32, Broadcast 2eSST |

|                                         | 0x22                              | A40/D32, Broadcast 2eSST |

Table 2.4: Extended Address Modifier Code

# 2.6.2 Address Modes

In the 2eSST standard, the XAM codes are used to define the address mode. For 6U implementations, one address range is defined for A32 type transactions and another for A64 type transactions. During an A32 transaction, the address is provided on signal lines A[31:8] during address phase one and A[7:4] during address phase two. During an A64 transaction, the address is provided on signal lines D[31:0] and A[31:8] during address phase one and A[7:4] during address phase one and A[7:4] during address phase one and A[7:4] during address phase two.

For 3U implementations, two address ranges are defined: A32 and A40. During an A32 transaction, the address is provided on signal lines D[7:0] and A[23:8] during address phase one and A[7:4] during address phase two. During an A40 transaction, the address is provided on signal lines D[15:0] and A[23:8] during address phase one and A[7:4] during address phase two.

Usage of the supervisory/non-privileged and the program/data sub-modes are no longer necessary, with the very large A40 and A64 address ranges. These large address ranges will most likely provide enough space to map the memory into special functional groups, if that is required by the specific application.

# 2.6.3 Transfer Rates

In the 2eSST standard, the maximum transfer rate is specified on data lines D[3:0] for a 6U implementation and data lines D[11:8] for a 3U implementation. The transfer rate is specified during address phase two (refer to Table 2.1 and Table 2.2). Boards using the 6U implementation transfer 64-bits (eight bytes) per transfer and transfer rates of 160, 267 and 320 MB/s are defined. Boards using the 3U implementation transfer 32-bits (four bytes) per transfer and transfer rates of 80, 133 and 160 MB/s are defined. The minimum cycle time is the same for 3U and 6U implementations but the maximum data transfer rate for a 3U implementation is half the maximum data transfer rate for a 6U implementation. This is because the data bus width in a 3U implementation is half width of a data bus in a 6U implementation. The 2eSST transfer rates for a 3U implementation are defined in Table 2.5. The 2eSST transfer rates for a 3U implementation are defined in Table 2.6

| Transfer<br>Rate Code | 6U<br>Transfer<br>Rate<br>(MB/s) | Nominal<br>Strobe<br>Width<br>(ns) | Maximum<br>Strobe<br>Frequency<br>(MHz) | Minimum<br>Strobe<br>Period<br>(ns) | Nominal<br>Strobe<br>Duty Cycle<br>(%) | Mnemonic |

|-----------------------|----------------------------------|------------------------------------|-----------------------------------------|-------------------------------------|----------------------------------------|----------|

| 0x0                   | 160                              | 50                                 | 10                                      | 100                                 | 50                                     | SST160   |

| 0x1                   | 267                              | 30                                 | 16.67                                   | 60                                  | 50                                     | SST267   |

| 0x2                   | 320                              | 25                                 | 20                                      | 50                                  | 50                                     | SST320   |

| 0x3-0xF               | Reserved                         | Reserved                           | Reserved                                | Reserved                            | Reserved                               | Reserved |

Table 2.5: 6U 2eSST Transfer Rates

Table 2.6:

3U 2eSST Transfer Rates

| Transfer<br>Rate Code | 3U<br>Transfer<br>Rate<br>(MB/s) | Nominal<br>Strobe<br>Width<br>(ns) | Maximum<br>Strobe<br>Frequency<br>(MHz) | Minimum<br>Strobe<br>Period<br>(ns) | Nominal<br>Strobe<br>Duty Cycle<br>(%) | Mnemonic |

|-----------------------|----------------------------------|------------------------------------|-----------------------------------------|-------------------------------------|----------------------------------------|----------|

| 0x0                   | 80                               | 50                                 | 10                                      | 100                                 | 50                                     | 3USST80  |

| 0x1                   | 133                              | 30                                 | 16.67                                   | 60                                  | 50                                     | 3USST133 |

| 0x2                   | 160                              | 25                                 | 20                                      | 50                                  | 50                                     | 3USST160 |

| 0x3-0xF               | Reserved                         | Reserved                           | Reserved                                | Reserved                            | Reserved                               | Reserved |

During address phase three, the slave can terminate the transfer with a slave error if it is unable to perform the requested transfer at the specified transfer rate.

The transfer rate specified is defined as a maximum transfer rate. The transmitter can transmit at a lower rate than specified. The transmitter can also throttle its transfer by momentarily reducing the transfer rate or stopping the transfer. However, transmitting below the specified transfer rate defeats the purpose of a high transfer rate protocol and should be avoided.

# 2.6.4 Known Length 2eSST Transfers

With many of the new microprocessors that employ caching architectures, as well as DMA controllers, the size of the data being written or requested is known in advance. The cycle count is presented on address lines A[15:8] during address phase two (refer to Table 2.1 and Table 2.2). This effectively informs the slave in advance of the amount of data that it is requested to receive in a write transaction or the amount of data it is to supply in a read request. The cycle count value sent is the beat count divided by two. There are two data beats in each cycle. For example, a cycle count of 0x00 = 0 data beats, a cycle count of 0x01 = 2 data beats, and a cycle count of 0x80 = 256 data beats.

Boards using the 6U implementation perform data transfers with 64-bit data words (eight bytes per transfer). The beat count represents the number of eight byte transfers. The byte count is the equal to the beat count times eight. The maximum cycle count is 128. For 6U implementations, this limits the transfer size to 2048 bytes (128 cycles \* 2 data beats per cycle \* 8 bytes per data beat).

Boards using the 3U implementation perform data transfers with 32-bit data words (four bytes per transfer).

| Draft S | <u>tandard</u> | for | Trial | Use |

|---------|----------------|-----|-------|-----|

|         |                | 17  | 7     |     |

The beat count represents the number of four byte transfers. The byte count is the equal to the beat count times four. The maximum cycle count is 128. For 3U implementations, this limits the transfer size to 1024 bytes (128 \* 2 data beats per cycle \* 4 bytes per data beat).

During write transfers, the master can transfer any even number of beats up to but not exceeding the beat count. During read transfers, the slave can transfer any even number of beats up to but not exceeding the beat count. The transmitter must not cross a 2K address boundary.

During address phase three, the slave can suspend the transfer if it is unable to perform the requested transfer at the present time. For example, if the slave's buffer is still full from a previous transfer, it can suspend the transfer and the master will retry the transfer at a later time. 6U slaves are required to support transfers up to 2048 bytes and 3U slaves are required to support transfers up to 1024 bytes.

# 2.6.5 Geographic Address

During address phase two, address lines A[20:16] are used to carry the Geographic Address (GA) of the master (refer to Table 2.1 and Table 2.2). If this feature is not implemented, the value must be 0. The Geographic Address is defined in Chapter 3 of the VME64x standard.

# 2.6.6 Subunit Number

During address phase two, address lines A[31:24] for 6U implementations and data lines D[7:0] for 3U implementations are used to carry the subunit number of the master (refer to Table 2.1 and Table 2.2). If this feature is not implemented, the value must be 0. If a VME board has multiple masters which perform 2eSST transfers, each master can be assigned a different subunit number.

# 2.6.7 Odd Bit

During address phase two, data line D[4] for 6U implementations and data line D[12] for 3U implementations are used to carry the odd bit. During a write transfer, the odd bit is set by the master to indicate that the data transferred during the last data beat is invalid. The 2eSST draft standard does not define how the slave handles the invalid data.

# 2.6.8 Broadcast Transfer Address Phase

Broadcast transfers are indicated by the XAM codes as defined in Table 2.4. There are several differences between a regular address phase and a broadcast transfer address phase. During a regular address phase, the selected slave (responding slave) responds by asserting the DTACK\* signal. However, during a broadcast transfer there may be multiple selected slaves and all of them cannot respond to the transfer. The selected slaves, during a broadcast transfer, do not respond to the master and they are considered participating slaves. The master generates the DTACK\* signal during the address phase of a broadcast transfer. The address phase of a broadcast transfer has the same timing diagram as a regular address phase. However, since the participating slaves do not respond to the master, they are not able to control the timing of the address phase. Therefore, the minimum time from DS0\* to DTACK\* has been increased to allow the participating slaves sufficient time to track the address phase. The participating slaves must be designed to work within this time.

The participating slaves can request a retry of the transfer by asserting the RETRY\*/RESP\* signal during address phase three. During the address phase three, the participating slaves are allowed to assert the BERR\* signal to indicate an error condition. Since the RETRY\*/RESP\* and BERR\* signals from the participating slaves are not interlocked with the master, the participating slaves must drive the RETRY\*/RESP\* or BERR\* signals within the specified time or the master may not receive the signal.

There are two levels of decoding associated with broadcast transfers. The broadcast slaves must decode the VMEbus address and address modifier codes like regular slaves. However, in the case of broadcast slaves, there may be more than one addressed slave. Address bits A[21:1] during address phase three carry the slave select signals that define which slaves are selected and will receive the broadcast data. Each of the 21 possi-

**Draft Standard for Trial Use**

18

ble slaves is assigned a unique select bit. The geographic address is used to define the slaves unique select bit. The geographic address GA=1 corresponds with address bit A[1], GA=2 corresponds with address bit A[2] and so on. Therefore, the slave in slot one (GA=1) will respond to a broadcast transfer if it is selected during address phase one and address bit A[1] is asserted during address phase 3.

# 2.7 Data Phase

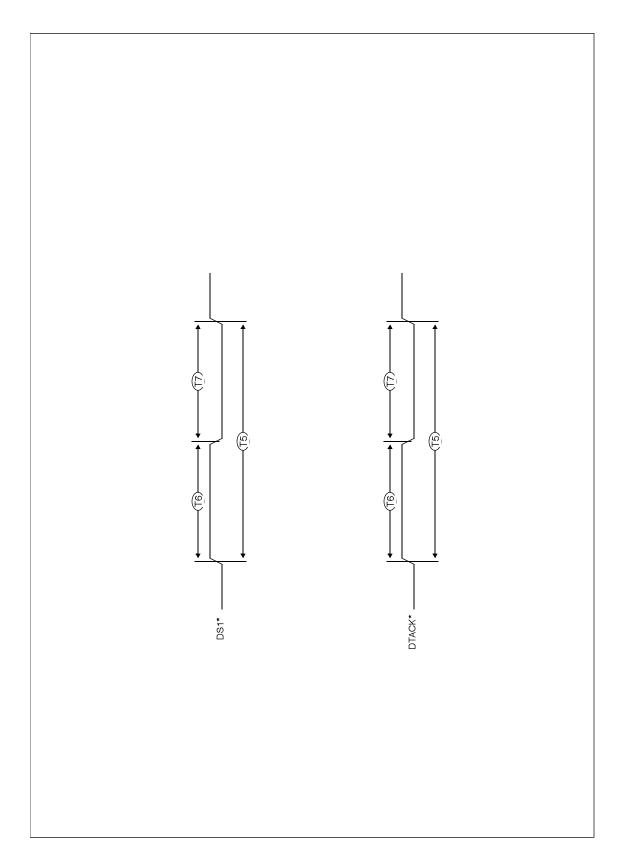

The protocols defined in the VME, VME64 and VME64x standards utilize a handshake protocol whereby data strobes (DS1\* and DS0\*) are acknowledged by DTACK\*. The receipt of DTACK\* by the master causes the data strobes to be removed which in turn causes DTACK\* to be removed. Once DTACK\* is deasserted, a new cycle can begin. The protocols defined in the VME and VME64 standards require four delays through the drivers, backplane and receivers plus the settling time of the backplane. The 2eVME protocol defined in the VME64x standard improves upon this by using both edges of DS1\* and DTACK\* to qualify the data. This doubles the throughput, but performance is limited by the requirement for an acknowledgment from the receiver of the data.

The 2eSST protocol has an address phase which is similar to the 2eVME address phase. After the address phase, however, the 2eSST transmitter sends the data along with a delayed strobe (either DS1\* or DTACK\*). The transmitter does not wait for any acknowledgments from the receiver and both edges of the strobe are used. Therefore, data can be streamed at much higher rates. For write transfers (where the master is the transmitter of data), DS1\* is used to qualify the data. For read transfers (where the slave is the transmitter of data), DTACK\* is used to qualify the data. DS0\* is not used as a strobe during the 2eVME or 2eSST data phase.

A consequence of the source synchronous nature of the 2eSST protocol is that the receiver of the data no longer has the ability to throttle the data transfer. In traditional VME block transfer reads, the master (the receiver of data) could throttle the transfer by controlling its assertion/deassertion of DS0\*/DS1\*. The slave (the receiver of data) could throttle writes by controlling DTACK\*. In the 2eSST protocol, only the transmitter of data can throttle the transfer. This implies that the 2eSST receiver (master during reads, slave during writes) must be able to accept the data at the rate it is sent.

# 2.7.1 Broadcast Transfer Data Phase

During the data phase of a broadcast transfer the master transmits the data and the participating slaves receive the data. During the data phase, participating slaves are allowed to assert BERR\* signal to indicate an error condition.

# 2.8 Transfer Termination

2eSST transfers are terminated by the transmitter. The receiver does not have the ability to terminate the transfer. Termination during error conditions is defined in the next section.

Transfers always terminate on an even beat. However, during a read operation the transmitter can indicate that the data in the last even data beat of the transfer is invalid. The invalid data indication accommodates slaves which are transferring data generated by external sources and do not have an even number of data words to transmit.

Terminating on an even beat helps achieve two of the objectives of the 2eSST protocol; it minimizes design complexity while maximizing throughput. By not allowing termination at odd beats, 2eSST state machines need not be designed for the special case where the transfer stops with the strobes in the asserted position necessitating a "clean-up" dummy cycle to return the strobes to the negated state. In addition, the number of test conditions a design must be verified under is reduced. By removing the potential for a dummy cycle, and by removing the requirement to monitor for terminations on every cycle, the state machines will also be able to run faster.

19

During a write transfer, the master controls the 2eSST address phase and the data phase. During the write data phase, the master sends data to the slave using DS1\* as a strobe to qualify the data. The master terminates a write transfer by stopping the data transmission and then negating DS0\*. The slave will respond by negating DTACK\*. The master will always terminate on an even beat count. The 2eSST protocol allows the master to terminate the write transfer at any time, even before the beat count is reached. This can be used for a variety of special type applications and situations.

During a read transfer, the master controls the 2eSST address phase and the slave controls the data phase. During the data phase, the slave is in control and sends data to the master using DTACK\* as a strobe to qualify the data. The slave terminates a read transfer by stopping the data transmission and then asserting RETRY\*/RESP\* and BERR\*. The master will respond by negating DS0\*. The slave will always terminate on an even beat count. The 2eSST protocol allows the slave to terminate the read transfer at any time, even before the beat count is reached. This can be used for a variety of special type applications and situations.

During a read transfer, the slave can indicate that the last data beat is not valid. The slave indicates the last data beat is not valid by asserting RETRY\*/RESP\* during the last data beat. The 2eSST draft standard does not define how the master handles the invalid data. The master can pass the invalid data to memory and set a status bit that indicates the last data beat is not valid.

# **2.9 Slave Error Termination**

As with other protocols, a slave error termination is also included with 2eSST. This permits the slave to relay some error condition back to the master. Identification of the particular error condition, and actions taken is not covered in this draft standard. During a read transfer a slave indicates an error termination by stopping the transfer, driving RETRY\*/RESP\* high and asserting BERR\*. During a write transfer, a slave indicates an error termination by asserting BERR\*.

During broadcast transfers, the BERR\* signal from the participating slaves is not interlocked with the master. Therefore, the participating slaves must drive the BERR\* signal within the specified time or the master may not receive the signal. A minimum time is specified between when the master negates DS0\* and when it negates DTACK\*. This provides a defined time period, after the last data beat is sent, in which the participating slave can assert a BERR\* and be sure the master will receive it.

# 2.10 Bus Time Out Timer

The 2eBTO timer defined for the 2eVME protocol also supports the 2eSST protocol and is the preferred timer. If the VMEbus BTO timer is used, the following items must be considered. During a 2eSST transfer, DS0\* is held low during the entire data transfer cycle. The transfer size of the 2eSST transfer must be selected to allow the transfer to complete before the timer expires.

# Chapter 3

# **Requirements**

This chapter defines the requirements for the 2eSST protocol in terms of rules, recommendations, suggestions, observations, and permissions.

# 3.1 Transceivers, Connectors and Backplanes

## Rule 3.1:

2eSST boards SHALL use, at a minimum, transceivers compatible with the transceivers specified in ANSI/VITA 1-1994, VME64 Specification.

## Recommendation 3.1:

2eSST boards SHOULD use higher performance bus transceivers with improved drive current, skew, and tighter receiver thresholds on all address, data and control bus signal lines.

## Rule 3.2:

System integrators using the 2eSST protocol **SHALL** ensure that the proper VME64 or VME64x backplane and boards loaded into the system will allow for monotonic rising and falling bus signals through the threshold region of the receiver.

## **Observation 3.1:**

Because the 2eSST protocol requires monotonic rising and falling edges of the bus signals at the receiver and low skew between the bus signals, only backplanes qualified by the manufacturer to be 2eSST compatible should be used.

## **Observation 3.2**

The bus signals can have non-monotonic rising and falling edges at the driver. A board that monitors the signals that it drives must be prepared for non-monotonic edges.

## Rule 3.3:

Boards using the 2eSST protocol SHALL support the RETRY\*/RESP\* line as defined in Section 2.2.

# Rule 3.4:

The 160-pin connector SHALL be used on boards and backplanes that support the 2eSST protocol.

# **Observation 3.3:**

The 160-pin connector provides additional ground pins that will improve the signal quality which is important to boards running high speed protocols such as 2eSST.

# **3.2 Address Phase Protocol**

The 2eSST protocol uses the three phase address transfer developed for 2eVME. This three phase address transfer is indicated by AM code 0x20 (for 6U implementations) and 0x21 (for 3U implementations). Within the first phase of this address transfer is a field, the XAM (Extended AM) code that indicates what protocol is to be used once the address transfer completes. The VME64x standard defines several of the XAM codes for 2eVME. This draft standard defines four additional XAM codes for the 2eSST protocol which are defined in Table 2.4.

**Draft Standard for Trial Use**

21

#### Rule 3.5:

A master using the 6U implementation **SHALL** transfer the information defined in Table 2.1 on the address and data lines during the address transfer phase. A master using the 3U implementation **SHALL** transfer the information defined in Table 2.2 on the address and data lines during the address transfer phase.

### Rule 3.6:

All address and data lines **SHALL** be at logical zero for features which are not implemented or are part of reserved fields.

### Rule 3.7:

Starting addresses SHALL be aligned on 16-byte boundaries (i.e. 128-bit aligned).

### Rule 3.8:

2eSST address timing **SHALL** be as defined in Table 3.1 and Table 3.2, as measured at the connector on the backplane.

## Rule 3.9:

2eSST address transfer phase **SHALL** be as defined in Figure 3.1 through Figure 3.4.

### **Observation 3.4**

The address phase protocol and timing for the 2eSST protocol is the same as in the 2eVME protocol. The address phase of a 2eSST broadcast is the same as a non-broadcast 2eSST address phase except the slaves do not respond. The interpretation of some of the data fields presented during the 2eSST address phase is different than those presented during the 2eVME address phase.

## Rule 3.10:

BERR\* **SHALL** only be asserted on the first or third address phase instead of toggling DTACK\*. See Figure 3.3 and Figure 3.4.

## Rule 3.11:

DTACK\* SHALL be the only valid response during address phase two.

## Rule 3.12:

Masters **SHALL** ignore RETRY\*/RESP\* during address phase one and two, and BERR\* during address phase two.

#### **Observation 3.5:**

Slave error and slave suspend operations are not supported during address phase two.

#### Rule 3.13:

RETRY\*/RESP\* SHALL only be asserted during address phase three.

#### **Observation 3.6:**

RETRY\*/RESP\* is not asserted in the first and second address phases.

#### **Observation 3.7:**

If RETRY\*/RESP\* is asserted before DTACK\* is toggled on the third address phase, the master interprets that response as indicating that the slave is suspending the operation but the master can expect data when it tries again. This can also be interpreted as a slave suspend response. See Figure 3.2.

#### **Observation 3.8:**

Since the target address is in two parts, the target device generates DTACK\* during the first phase of the address transfer if that portion of the address is recognized. The lowest byte of the address comes in the second address phase and therefore cannot be used as part of the address decode. The low byte only specifies an internal address.

#### **Observation 3.9:**

The Geographical Address (GA) in the second address phase provides a mechanism to identify the bus master.

#### **Observation 3.10:**

The subunit number, transferred in the second address phase, provides a mechanism for identifying which part of a master initiated a transaction. In the case of a VME module with several processors, it could be the processor number.

#### Rule 3.14:

2eSST masters and slaves SHALL use the AM and XAM codes as defined in Table 2.4.

#### **Observation 3.11:**

Address modifier codes 0x20 and 0x21 have been defined in the VME64x standard to specify a threephase address transfer. These AM codes are shared with the 2eVME protocol, and are expected to be shared with other protocols as they are developed over time.

#### Rule 3.15:

If a targeted 2eSST slave is unable to operate at the transfer rate defined by the transfer rate code, it **SHALL** terminate the transfer with a slave error during phase three of the address transfer.

#### **Recommendation 3.2:**

2eSST masters and slaves SHOULD also support 2eVME transfers.

#### **Observation 3.12:**

Recommendation 3.2 ensures that a 2eSST capable board should be able to perform slower 2eVME operations if the board is placed in a system that cannot support 2eSST transfers.

#### Rule 3.16:

6U 2eSST masters supporting SST320 SHALL also support SST267 and SST160. 3U 2eSST masters supporting 3USST160 SHALL also support 3USST133 and 3USST80.

#### Rule 3.17:

6U 2eSST masters supporting SST267 **SHALL** also support SST160. 3U 2eSST masters supporting 3USST133 **SHALL** also support 3USST80.

#### Permission 3.1:

The 2eSST draft standard does not define a minimum transfer rate. The transmitter **MAY** transmit at a rate below the maximum indicated rate for a portion or all of the transfer.

### **Observation 3.13:**

Since a minimum transfer rate is not specified, a master may claim to support a transfer rate but actually transmit at a lower rate. For example, a master may claim support for the SST267 rate but actually transmit at SST160.

#### Permission 3.2:

6U 2eSST slaves **MAY** support any combination of SST320, SST267 and SST160. 3U 2eSST slaves **MAY** support any combination of 3USST160, 3USST133 and 3USST80.

#### Rule 3.18:

The mnemonics defined in Table 2.5 and Table 2.6 **SHALL** be used to indicate a product's support for that level of 2eSST performance.

#### Permission 3.3:

Boards using the 6U implementation **MAY** also participate in 3U 2eSST transfers using the applicable AM and XAM Codes defined for 3U 2eSST transfers.

## Rule 3.19:

The cycle count in the second address phase specifies the maximum number of cycles that **SHALL** occur during the transaction. The cycle count is the number of data beats divided by two. For example, a cycle count of 0x00 = 0 data beats, a cycle count of 0x01 = 2 data beats, and a cycle count of 0x80 = 256 data beats. The maximum cycle count is 128 cycles. Slaves **SHALL** support a cycle count of 0-128 cycles.

#### Permission 3.4:

The cycle count MAY be zero which indicates that no data will be transferred.

#### **Observation 3.14:**

During a write transfer, the slave can not throttle the master. Therefore, the slave must be designed to receive a 128 cycle transfer.

#### **Observation 3.15:**

Since the transmitter can only transfer an even number of beats, the modulo 2 number for the beat count is compatible with the specified operation.

#### **Observation 3.16:**

The cycle count represents a maximum value only. During 2eSST transfers, the receiver must be prepared for an early termination.

#### **Observation 3.17:**

The cycle count is provided to allow slaves to optimize their performance. During reads, the cycle count tells the slave how much data to transmit. During writes, the slave can use this field to determine if sufficient room is available in its write posting FIFOs, and suspend the transaction if insufficient room is available. During a write transfer, it is not advisable for the master to indicate a cycle count that is larger than the intended transfer. It is possible the slave will needlessly suspend the transfer because it believes it does not have room in its buffer.

#### Rule 3.20:

Masters that are sending an odd number of valid data words **SHALL** set the odd bit, which is sent during address phase two.

#### **Observation 3.18:**

During a write transfer, the master can set the odd bit, which is transferred during address phase two, to indicate that the data transferred during the last data beat is invalid. This mechanism allows the master to transfer an odd number of data words to the slave.

**Draft Standard for Trial Use**

# 3.3 Data Phases

The data phase of 2eSST transfer presents the data on D[31:0] and A[31:0], (D[15:0] and A[15:0] for 3U implementations) in the same manner as MBLT and 2eVME transfers. LWORD\* has been defined as A[0] which is the same as in MBLT and 2eVME. During write transactions, the data is transmitted from master to slave. During read transactions, the data is transmitted from slave to master. Regardless of which device is transmitting the data, the data is sent in the same manner: data qualified with a strobe, followed by the next data qualified with the opposite edge of the same strobe. When the master is transmitting the data, DS1\* is used as the qualifying strobe. When the slave is transmitting the data, it uses DTACK\* to qualify the data.

The transmitter of data does not await acknowledgment of the data beat from the receiver. Instead it continuously transmits the data at a rate indicated by the transfer rate code.

## Rule 3.21:

2eSST data transfer phase SHALL be as defined in Figure 3.5 through Figure 3.9.

### Rule 3.22:

The transmitter **SHALL** transmit the data with setup and hold times to the strobe as defined in Table 3.1 and with the strobe timing defined in Table 3.3.

### **Observation 3.19:**

The 2eSST protocols operate with strobes that switch in the center of the data window halfway between the permitted occurrence of data transitions. This has several benefits:

- 1. The strobe (which is the single most important timing signal qualifying the data) switches when the data lines are quiet and there is minimal cross talk and ground bounce to affect the strobe timing.

- 2. The source skew of the strobe is minimized since the delay between data and strobe can be done very precisely utilizing the opposite phase of the transmit clock or a 2x clock. If the opposite phase of the transmit clock is used, the duty cycle must be controlled.

- 3. Because the skew in a system is symmetric (data can skew either side of the strobe), the data will be guaranteed to be valid when the strobe reaches the receiver. The strobe then can be used to qualify the data with minimal logic.

- 4. Since the strobe switches in the center of the data window (at the transmitter), the slower data rates have improved setup and hold times.

Both edges of the strobe are used to qualify the data. To ensure that the strobes end up in the inactive state and to simplify state machine design, an even number of data beats will always be transmitted.

#### **Observation 3.20:**

The 2eSST design specifies that the slowest data has been presented to the receiving registers by one set-up time before the fastest strobe can arrive to clock the registers. It also specifies that the slowest strobe has already clocked the receiving registers by one hold time prior to the fastest data changing at the registers.

#### Rule 3.23: