## Approved as an American National Standard by

# American National Standard for IP Modules

#### Secretariat

#### **VMEbus International Trade Association**

Approved July 16, 1996 American National Standards Institute, Inc.

### YMEDOS INTERNATIONAL TRADE ASSOCIATION

7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260-3415 USA PH: 602-951-8866, FAX: 602-951-0720 E-mail: info@vita.com, URL: http://www.vita.com

# American National Standard for IP Modules

Secretariat

**VMEbus International Trade Association**

Approved July 16, 1996 American National Standards Institute, Inc.

#### Abstract

This standard defines a versatile module, known as an "IP module." These modules provide a convenient method of implementing a wide range of I/O, control, interface, slave processor, analog and digital functions. IP modules, about the size of a traditional business card, mount parallel with a host Carrier board, which provides host processor or primary bus interfacing, as well as mechanical means for connecting the IP module's I/O to the outside world. Typical Carriers include standalone processors, DSP based carriers, as well as desktop buses and VME based boards. This specification includes mechanical, host bus electrical, and logical definition of I/O space, memory space, identification space, interrupts, DMA, and reset functions. Two physical sizes, two fixed clock rates. and multiple data width sizes to 32-bits are defined.

## American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether they have approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standard Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

Published by

VMEbus International Trade Association 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260-3415

Copyright © 1996 by VITA, the VMEbus International Trade Association. All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of the publisher.

Printed in the United States of America

ISBN 1-885731-05-1

**Foreword** (This foreword is not part of American National Standard ANSI/VITA 4-1994, IP Modules).

As VME became the industrial bus of choice in the 80s, the standard IC moved from a 20-pin MSI DIP to a VLSI high pin count surface mount device. Although the functionality of standard boards increased dramatically, the average selling price remained at about \$2500. This high per-slot cost prompted manufacturers to continue to place as much functionality on each board as possible, to keep the total slot and total system costs as low as possible. This trend increased the basic functionality granularity (the smallest purchasable function) 10 to 50 fold. It was no longer practical to purchase separately a small number of serial lines or a small amount of memory. Many manufacturers attempted to remedy this problem by offering proprietary "daughter modules" for their processor boards. At least 20 different such proprietary offerings were on the market by the end of the 1980s.

At this time GreenSpring Computers, under the technical direction of Kim Rubin, created a module with the specific design and intent that it become an open, widely accepted standard. GreenSpring Computers introduced the module and its specification as an open standard at BUSCON in 1988.

When the modules were introduced, GreenSpring incorporated features that were found in only a few, if any, other modules:

- Up to four modules fit on one VME or PC-AT board, for high modularity

- Bus and processor independent; supported both Motorola and Intel byte ordering

- · Simple, synchronous interface made Modules and Carriers easy to design

- · Rugged mechanical mounting, for ease of use and high reliability

- Defined ID space for configuration management

- Low cost

The concept caught on, and by 1994 over 80 companies were designing and offering products to this standard, on at least seven standard buses. GreenSpring called their modules "IndustryPacks®," but each manufacturer was free to use whatever trade name they wished. The modules are called "IP Modules," a term that is now in the public domain. This standard is a direct result of that work.

In 1991 Motorola Computer Group incorporated the IP Module specification into its 68040 based MVME162, implementing four IP Module positions in a single VME slot. This helped propel the acceptance of the specification. For the remainder of this document, the modules will be identified as "IP Modules." Manufacturers and users are encouraged to use this term for the generic identification of these modules.

At the start of 1994 a formal standards committee was put together under the VSO, the VITA Standards Organization, which had received accreditation as a standards organization under ANSI. Most of the committee's work has been done via internet, which has proven effective. The purpose of the committee is to validate and clarify the existing specification. In particular, timing details for 32 MHz and DMA operation are being clarified. Also, the specification was reformatted, with numbering added for easier reference and formality.

There are four appendices in this standard. All are informative and are not considered part of this standard.

#### Scope of the Standard

This document define the following elements of IP Modules:

- Electrical Interface of the Logic connector, including voltage levels, loading, pin definition, cycle types, timing diagrams, and state diagrams;

- · Mechanical size and mounting of the IP Modules, for single-size and double-size;

- Mechanical and electrical requirements of the IP Module Carrier Board;

- The mechanical I/O connector;

- The minimum contents for the ID space;

- Permissible feature combinations.

The following elements are beyond the scope of this Standard:

- I/O pin assignment;

- I/O system wiring;

- · Regulatory compliance issues;

- System power;

- Host system architecture, processor, instruction set and byte ordering;

- System and application software issues;

- Definitions of any individual modules.

# **Table of Contents**

| 1. DESCRIPTION                             | 5   |

|--------------------------------------------|-----|

| 2. SIGNAL DESCRIPTIONS                     | 7   |

| 2.1. D00D15 [DATA BUS]                     | 7   |

| 2.2. A1A6 [ADDRESS]                        | 7   |

| 2.3. RESET*                                |     |

| 2.4. IOSEL* [I/O SELECT]                   |     |

| 2.5. MEMSEL* [MEMORY SELECT]               |     |

| 2.6. INTSEL* [READ INT VECTOR]             | 8   |

| 2.7. CLK [CLOCK]                           | 9   |

| 2.8. IDSEL* [IP MODULE IDENTIFICATION]     | 9   |

| 2.9. R/W* [DATA DIRECTION]                 |     |

| 2.10. ACK* [D ATA ACKNOWLEDGE]             |     |

| 2.11. BS0*BS1* [BYTE SELECT]               | .10 |

| 2.12. INTREQ0*INTREQ1* [INTERRUPT REQUEST] |     |

| 2.13. DMAREQ0*DMAREQ1* [DMA REQUEST]       |     |

| 2.14. DMACK* [DMA ACKNOWLEDGE]             |     |

| 2.15. DMAEND* [DMA TERMINATION]            |     |

| 2.16. ERROR* [IP MODULE ERROR]             |     |

| 2.17. STROBE* [FUNCTION STROBE]            |     |

| 2.18. GND [GROUND]                         |     |

| 2.19. +5V [+5 VOLTS]                       |     |

| 2.20. +12V, -12V [+12 VOLTS, -12 VOLTS]    |     |

| 2.21. RESERVED.                            | .15 |

| 3. CYCLE TYPES                             | 17  |

| 4. ADDRESSING CONVENTIONS                  | 19  |

| 4.1. A0 USAGE                              | 10  |

| 4.1. AU USAGE                              |     |

|                                            |     |

| 5. I/O SPACE                               | 21  |

| 6. MEMORY SPACE                            | 23  |

| 7. DIRECT MEMORY ACCESS                    | 25  |

|                                            |     |

| 7.1. I/O DMA CYCLES                        |     |

| 7.2. MEMORY DMA CYCLES                     | .26 |

| 8. INTERRUPT ACKNOWLEDGE                   | 27  |

| 9. ID ROM DATA                             | 2.9 |

|                                            |     |

| 9.1. ID ROM DATA FORMAT I                  |     |

| 9.2. ID ROM DATA FORMAT II                 | .32 |

| 10. 8 MHZ DATA TRANSFER CYCLE DETAILS      | 35  |

| 11. 32-BIT ACCESS                          | 37  |

| 12. 8 MHZ TIMING DETAILS                          | 39       |

|---------------------------------------------------|----------|

| 13. 32 MHZ OPERATION                              | 41       |

| 14. TEST CONDITIONS                               | 43       |

| 14.1. STANDARD TEST CONDITIONS                    |          |

| 15. PIN ASSIGNMENT                                | 45       |

| 16. ELECTRICAL INTERFACE                          | 47       |

| 16.1. 8 MHZ LOADING                               | 47<br>48 |

| 17. PHYSICAL DIMENSIONS                           | 49       |

| 18. ALLOWABLE COMBINATIONS OF FEATURES            | 53       |

| 18.1. FEATURE COMBINATIONS FOR CARRIER BOARDS     |          |

| 19. APPENDIX A - ID ROM CHECKSUM (INFORMATIVE)    | 77       |

| 20. APPENDIX B - METRIC EQUIVALENTS (INFORMATIVE) | 85       |

| 21. APPENDIX C - CONNECTORS (INFORMATIVE)         | 87       |

| 22. APPENDIX D - REVISIONS (INFORMATIVE)          | 89       |

| 22.1. REVISION CHANGE TO 1.0.E                    | 89       |

| 22.3. REVISION CHANGE TO 1.0.C                    |          |

| 22.5. REVISION CHANGE TO 1.0. A                   | 89       |

## **List of Tables**

| TABLE 1 | SIGNAL IDENTIFICATION                | 6  |

|---------|--------------------------------------|----|

| TABLE 2 | C Y CLE TYPES                        | 17 |

| TABLE 3 | ADDRESS SPACES BY CYCLE TYPE         | 17 |

| TABLE 4 | ID ROM DATA FORMAT I                 | 30 |

|         | ID ROM DATA FORMAT II                |    |

| TABLE 6 | PIN ASSIGNMENT OF SIGNAL NAMES       | 45 |

| TABLE 7 | CURRENT LOADING LIMITS OF IP MODULES | 48 |

# List of Figures

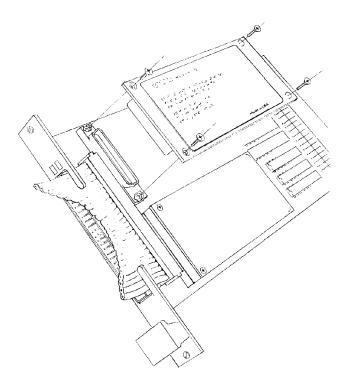

| FIGURE 1  | TWO IP MODULES MOUNTED ON 3U VMEBUS CARRIER       | 57 |

|-----------|---------------------------------------------------|----|

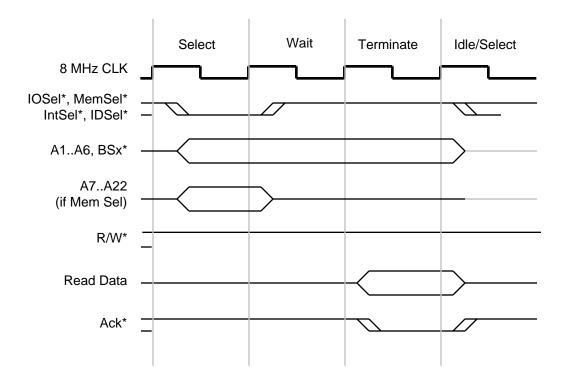

| FIGURE 2  | FASTEST 8 MHZ I/O WRITE CYCLE                     |    |

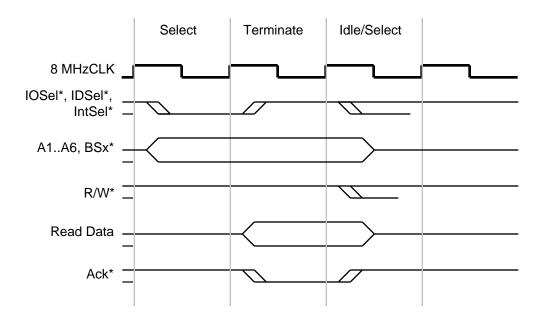

| FIGURE 3  | FASTEST 8 MHZ READ CYCLES.                        |    |

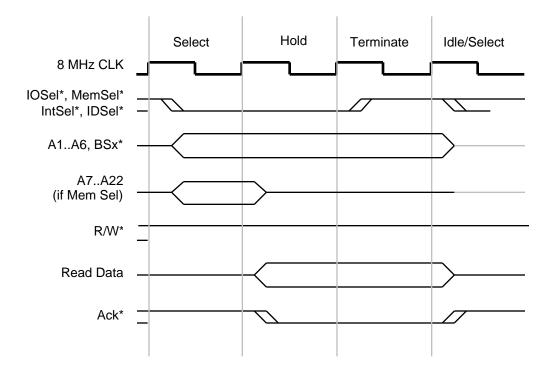

| FIGURE 4  | 8 MHZ READ CYCLE WITH HOLD STATE                  |    |

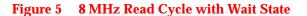

| FIGURE 5  | 8 MHZ READ CYCLE WITH WAIT STATE                  |    |

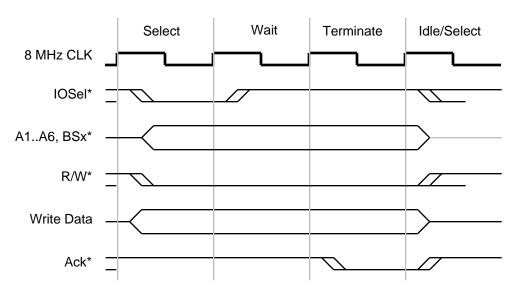

| FIGURE 6  | 8 MHZ I/O WRITE CYCLE WITH WAIT STATE             | 60 |

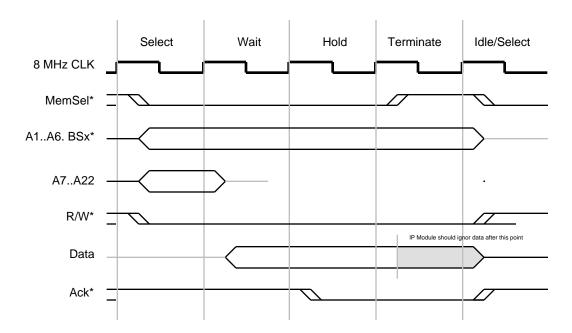

| FIGURE 7  | 8 MHZ MEMORY WRITE CYCLE WITH WAIT AND HOLD STATE | 60 |

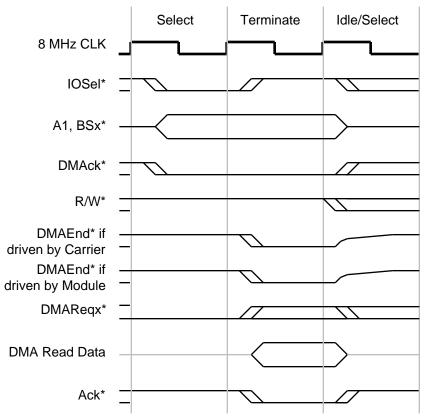

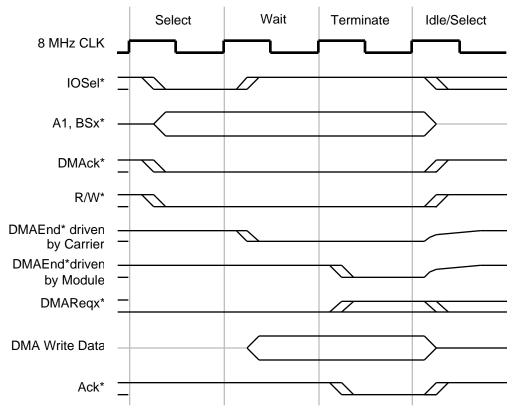

| FIGURE 8  | 8 MHZ DMA READ CYCLE                              |    |

| FIGURE 9  | 8 MHZ DMA WRITE CYCLE WITH WAIT STATE             |    |

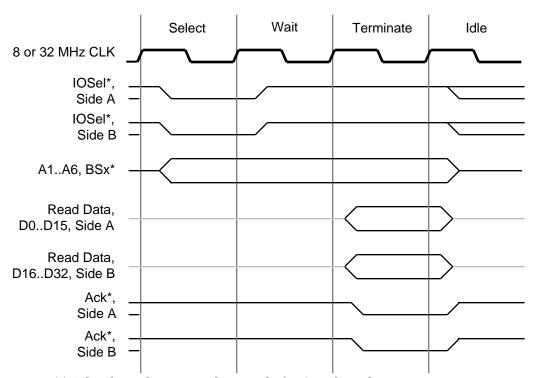

| FIGURE 10 | 32-BIT DOUBLE-SIZE OPERATION.                     | 63 |

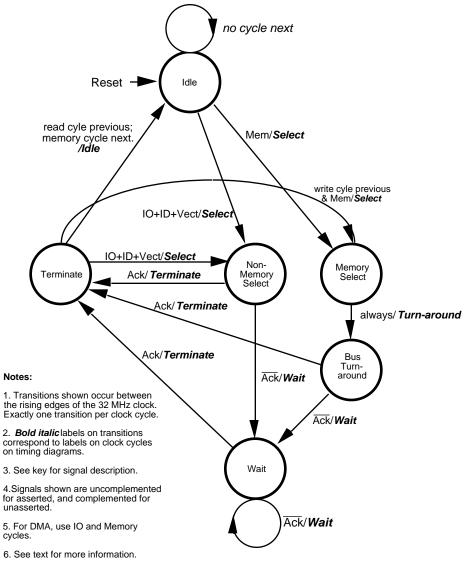

| FIGURE 11 | 8 MHZ STATE DIAGRAM                               |    |

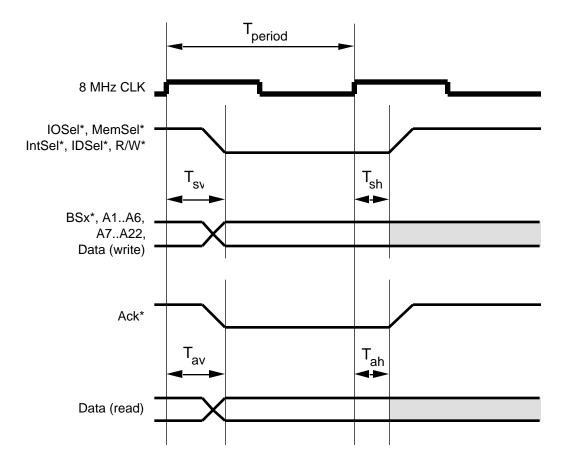

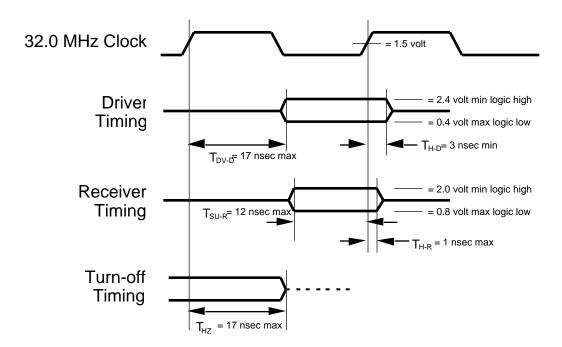

| FIGURE 12 | 8 MHZ DETAILED TIMING DIAGRAM                     | 65 |

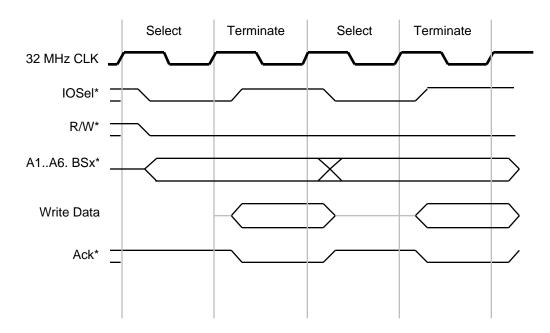

| FIGURE 13 | 32 MHZ TWO I/O WRITE CYCLES BACK TO BACK          | 66 |

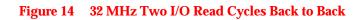

| FIGURE 14 | 32 MHZ TWO I/O READ CYCLES BACK TO BACK           |    |

| FIGURE 15 | 32 MHZ FASTEST MEMORY WRITE CYCLE                 | 67 |

| FIGURE 16 | 32 MHZ FASTEST MEMORY READ CYCLE                  | 67 |

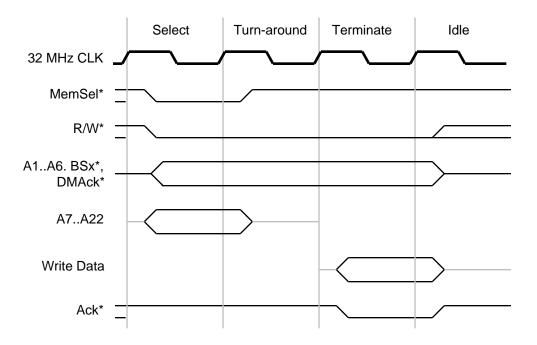

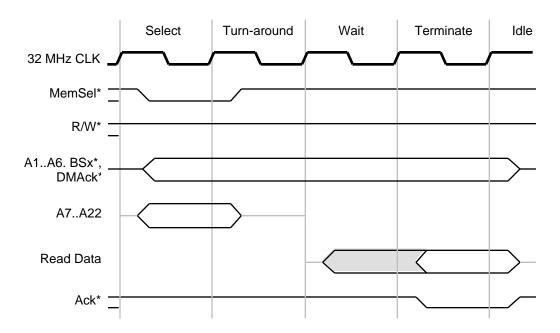

| FIGURE 17 | 32 MHZ MEMORY READ CYCLE WITH WAIT STATE          | 68 |

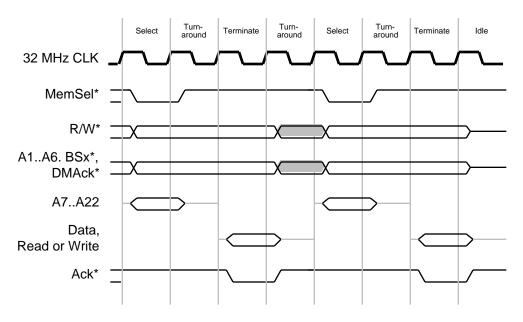

| FIGURE 18 | 32 MHZ TWO MEMORY CYCLES BACK TO BACK             | 68 |

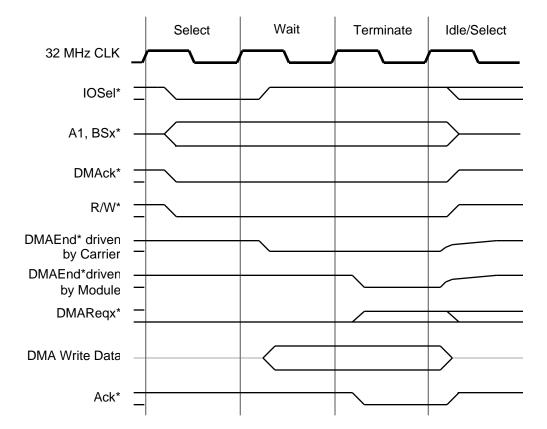

| FIGURE 19 | 32 MHZ DMA I/O WRITE CYCLE WITH WAIT STATE        | 69 |

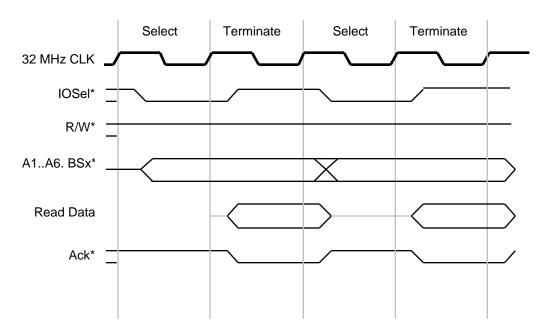

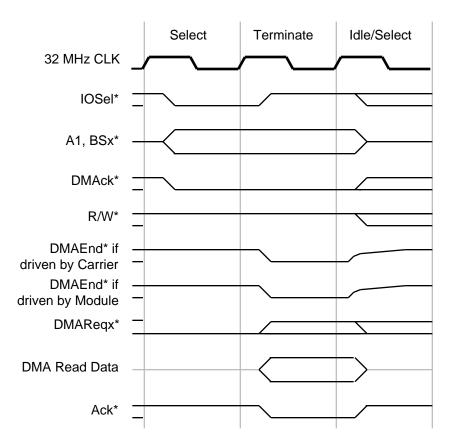

| FIGURE 20 | 32 MHZ DMA I/O READ CYCLE                         | 70 |

| FIGURE 21 | 32 MHZ STATE DIAGRAM                              | 71 |

| FIGURE 22 | 32 MHZ DETAILED TIMING                            | 72 |

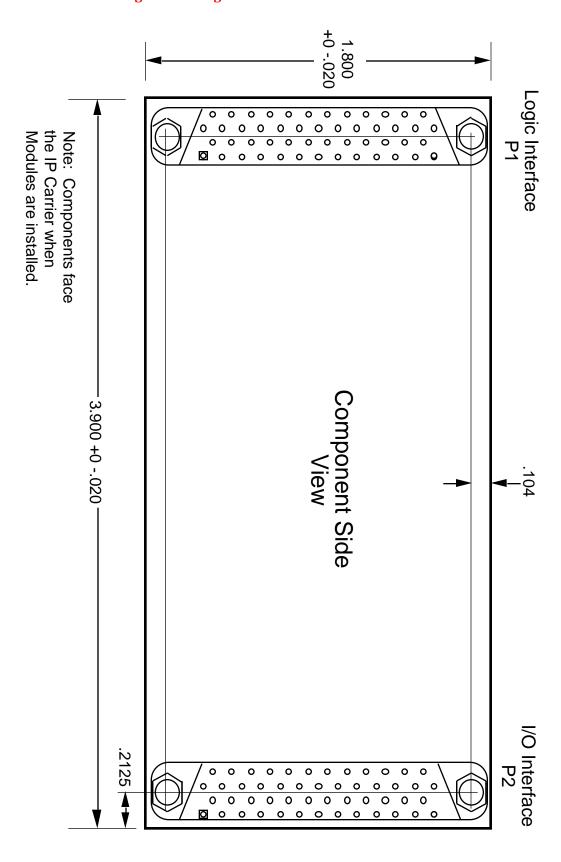

| FIGURE 23 | SINGLE-SIZE IP MODULE MECHANICAL OUTLINE          | 73 |

| FIGURE 24 | IP MODULE MECHANICAL DETAIL                       |    |

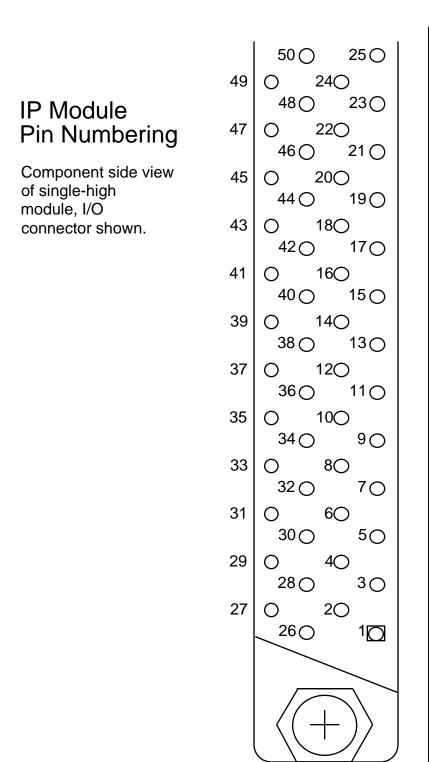

| FIGURE 25 | IP MODULE PIN NUMBERING                           | 75 |

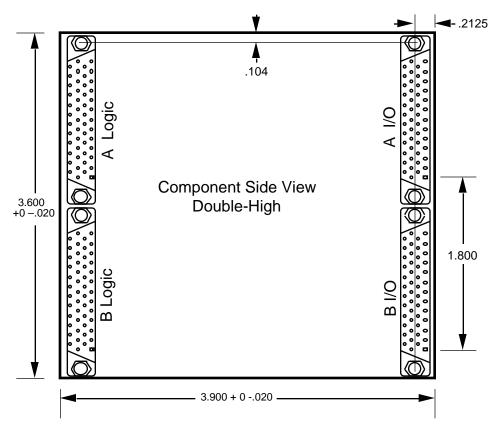

| FIGURE 26 | DOUBLE-SIZE MODULE MECHANICAL                     | 76 |

|           |                                                   |    |

## 1. Description

The IP Module is a versatile electronic module that provides a convenient level of modularity for implementing a wide range of I/O, control, interface, analog and digital functions.

Up to two IP Modules can be mounted on a 3U (single high) VMEbus board, up to four IP Modules on a 6U (double high) VMEbus or "C" size VXIbus board. IP Modules also fit conveniently on Macintosh II™ NuBus boards. In these busses, mounted IP Modules meet all applicable bus specifications. Up to six IP Modules may be used on larger carrier boards. Figure 1 shows a typical IP Module mounting arrangement (in this case, on a 3U VME board).

The IP Module specification is comprehensive. Memory is supported, as are interrupts and DMA. The basic IP Module interface—8 MHz, single-size—supports a continuous data rate of eight MB/second as four megatransfers per second using 16-bit word transfer size. Peak continuous data rate for a 32 MHz, 32-bit Module is 64 MB/second as 16 megatransfers per second using a 32-bit data transfer width. Each IP Module includes a configuration (ID) ROM. This ID information may be used by software for autoconfiguration.

IP Modules come in two sizes, single-size and double-size. The double-size appears electrically and mechanically as two adjacent IP Modules. This Specification describes the single-size IP Module unless explicitly stated otherwise.

Two connectors are used on each IP Module. One is dedicated to control of the IP Module, and is fully specified. This connector contains the Logic Interface, which is described in this document. This interface is generally thought of as a "bus," although not all signals are actually bussed. The other connector is provided for the IP Module's specific function. It's interface is called the I/O Interface. All 50 signals in the I/O Interface are defined by each IP Module. The connectors are an industry standard part. The connector pins are gold plated and fully shrouded; the connectors are keyed, assuring reliable, repeatable field installation.

Each IP Module communicates with its Carrier board via a single 50 pin connector. This connector contains address, data, clock, control and power lines. This "bus" is called the IP Module Logic Interface. This document is the specification for that interface.

All data transfers between the Carrier board and the IP Module are done synchronously. This provides a simple, reliable design. CMOS logic levels are used to keep power dissipation of both IP Modules and Carrier boards to a minimum.

#### **Features:**

- Simple, reliable electrical design (synchronous transfers)

- Simple, reliable mechanical design (shrouded, keyed connector)

- Mechanically compatible with 3U VME, 6U VME, NuBus, ISA, PCI and VXI

- ID ROM permits autoconfiguration, compatible with VXI and NuBus

- word (128 byte) I/O space per IP Module

- Up to 8 MB memory space per single-size IP Module

- Byte or word addressing

- Two interrupts per single-size IP Module

- Two DMA channels per single-size IP Module

- 64 Mbyte/second peak continuous data rate (32-bit, 32 MHz, I/O operation)

- 32-bit data width and 32 MHz clock options

**Table 1 Signal Identification**

| Function              | Name     | No of Pins | Class   |

|-----------------------|----------|------------|---------|

| Data Bus              | D00D15   | 16         | data    |

| Address               | A1A6     | 6          | address |

|                       |          | (Note 1)   |         |

| Reset                 | Reset*   | 1          | control |

| I/O Select            | IOSel*   | 1          | control |

| Memory Select         | MemSel*  | 1          | control |

| Read Int Vector       | IntSel*  | 1          | control |

| Clock                 | CLK      | 1          | clock   |

| Module Identification | IDSel*   | 1          | control |

| Data Direction        | R/W*     | 1          | control |

| Data Acknowledge      | Ack*     | 1          | control |

| Byte Select           | BS0*     | 2          | control |

|                       | BS1*     |            |         |

| Interrupt Request     | IntReq0* | 2          | control |

|                       | IntReq1* |            |         |

| DMA Request           | DMAReq0* | 2          | control |

|                       | DMAReq1* |            |         |

| DMA Acknowledge       | DMAck*   | 1          | control |

| DMA Termination       | DMAEnd*  | 1          | control |

| IP Module Error       | Error*   | 1          | control |

| Function Strobe       | Strobe*  | 1          | option  |

| Ground                | GND      | 4          | power   |

| +5 Volts              | +5V      | 2          | power   |

| +12 Volts             | +12V     | 1          | power   |

| -12 Volts             | -12V     | 1          | power   |

| Reserved              |          | 2          | reserve |

| Total                 |          | 50         |         |

An asterisk (\*) after the signal name means that the line is active low. All other signals are active high.

Note 1: During memory access cycles, the 16 data lines are used for the high order address lines (A7..A22).

## 2. Signal Descriptions

The following paragraphs discuss each of the signals used in the IP Module Logic Interface.

#### 2.1. **D00..D15** [Data Bus]

The 16 lines of the data bus are used to read and write data between the Carrier board and the IP Module. These lines are used for I/O, memory, DMA, interrupt vectors, and ID data. During memory addressing, these lines carry the high order 16 bits of the address (A7..A22). Data transfer is synchronous with CLK. During some transfers only the low order eight (D0..D7) lines are used. See the figures at the end of this document for timing details.

#### 2.2. A1..A6 [Address]

The six lines of the address bus are used for addressing I/O locations. These lines are the low order six lines during memory addressing. Only the Carrier board drives the address lines. The address lines are interpreted as "word" addresses. Byte writes are accomplished by using the Byte Select ( $BSx^*$ ) lines. A1 is used during interrupt acknowledge cycles and DMA acknowledge cycles to select which interrupt or DMA channel is being acknowledged. A1 through A5 are used to select which of 32 bytes or 32 words are being read during Read ID cycles. A6 must be low during ID space reads (for compatibility with future enhancements in the ID space).

The address lines are not used for selecting IP Modules. The four select lines (IOSel\*, MemSel\*, IntSel\* and IDSel\*) are used for this purpose. This may be interpreted as "geographic addressing," since the select lines are not bussed.

#### 2.3. **Reset\***

The active low Reset\* signal is driven from the Carrier board to the IP Modules to reset the circuitry to a known state.

Reset\* must be driven following power up for at least 200 milliseconds. There is no maximum time limit. When Reset\* is asserted to the IP Modules they must terminate any cycle in progress, remove any interrupt requests and DMA requests, and disable future interrupt and DMA requests (until enabled by software). Reset may be asserted asynchronously, but must be de-asserted synchronously.

Reset\* must also be asserted by the Carrier board if the power supplies fall below minimum specifications of the carrier board or host bus. +5 must be monitored; monitoring of other supplies is optional. This is required particularly so that the Reset\* signal may be used by an IP Module to safely switch to standby or fail-safe operation. Thus the Reset\* signal is a logical OR of "Reset" and "Power-Fail" functions.

Unless an IP Module has no local registers it must respond to Reset\*. If an IP Module has non-volatile memory, that memory need not be reset. However the IP Module's documentation must clearly state which locations and registers are affected by Reset\*.

An IP Module may take some time following the end of Reset until it is capable of responding . This time may be needed to load programmable logic, perform a self-test, internal calibration, internal initiation or other function. The IP Module's documentation must clearly state the maximum time necessary for the module to initialize, and what functions, if any, are available prior to the completion of the local initialization.

#### 2.4. IOSel\* [I/O Select]

The active low IOSel\* signal is one of four "select" lines driven by the Carrier board to enable the IP Module. This line is used for input or output cycles. These cycles use only the six address lines A1.. A6. Each IP Module thus occupies 64 words, or 128 bytes in the system I/O space.

Data width on I/O cycles is a function of the IP Module itself, and is generally fixed. If only eight bits are used by an IP Module, they must be the low order (D0..D7) data lines.

IOSel\* is unique to each IP Module; it is not bussed. An IP Module need not respond to IOSel\* if it has no I/O functions.

The byte select lines must be driven valid by Carrier boards. IP Modules are not obligated to examine the byte select lines during accesses in the I/O space, however.

An IP Module need not respond to IOSel\* if it has no functions in the I/O space. It need not decode any address lines that it does not need. Thus functions (registers) within an IP Module's I/O space may appear in multiple places within the 64 word I/O space.

IOSel\* is also used in I/O DMA cycles. For these cycles, DMAck\* is asserted simultaneously with IOSel\*. I/O DMA cycles are compelled. Each cycle is in response to a DMA Request from the IP Module. See DMA Section for more information.

#### 2.5. MemSel\* [Memory Select]

The active low MemSel\* signal is one of four "select" lines driven by the Carrier board to enable the IP Module. This line is used for memory read or write cycles. These cycles use up to 22 address lines to address up to eight MB per IP Module. The synchronous protocol uses the data lines to carry the high order 16 address signals during the first clock of the memory access cycle.

Memory write cycles use the two byte select signals (BS0\*, BS1\*). IP Modules, during memory read cycles may ignore the byte selects by driving both bytes, if desired. Carrier boards must drive the byte select signals valid on all memory cycles.

MemSel\* is unique to each IP Module; it is not bussed. An IP Module need not respond to MemSel\* if it has no memory.

MemSel\* is also used in Memory DMA cycles. For these cycles, DMAck\* is asserted simultaneously with MemSel\*. Memory DMA cycles are not compelled. These cycles indicate that the source of the cycle is a host DMA controller. See DMA Section for more information.

#### 2.6. IntSel\* [Read Int Vector]

The active low IntSel\* signal is one of four "select" lines driven by the Carrier board to enable the IP Module. This line is used for reading the IP Module's interrupt vector during an interrupt acknowledge cycle. A1 is used to indicate if the acknowledge is for IntReq0\* (A1 is Low) or IntReq1\* (A1 is High). The interrupt vector may be eight or 16 bits, but typically is eight.

IntSel\* is unique to each IP Module and is not bussed. An IP Module need not respond to IntSel\* if it has no interrupt requests asserted. However an IP Module should not remove interrupt requests without a specific action from the host Carrier board.

#### 2.7. CLK [Clock]

This signal is a 50 percent duty cycle 8.0 MHz or 32.0 MHz clock driven to the IP Module by the Carrier board. All data transfers are synchronous to this clock. The signals involved in a data transfer are changed relative to the rising edge of the clock. Signals generated by the Carrier board are typically sampled by the IP Modules on the next rising edge of the clock. Signals generated by the IP Modules are sampled by the Carrier board on the rising edge of the clock. See Figure 9 for timing details.

Recommendation 2-1: It is recommended that Carrier board designers use a series terminated CLK driver to avoid reflections on this key signal. For traditional .062 inch thick FR4 circuit boards, six to eight layers with internal power and ground planes and typical design rules of .007 trace and .008 gap, 33 has been found to be a good value. A separate series termination resistor for each IP Module is recommended. Carrier board designers may wish to consider that in such a design the IP Module will see the CLK edge delayed slightly from the edge at the output of the CLK driver.

Recommendation 2-2: It is recommended that IP Module designers keep in mind that the CLK signal may not be as clean as desired. Also that there is likely to be some skew between the edge received by the IP Module and the edge known to the Carrier board. Therefore, conservative timing design is recommended.

Low level timing is not the same for 8 MHz and 32 MHz interfaces. Also, the basic cycle state machine is slightly different for 8 MHz and 32 MHz operation. IP Modules must be specified for operation at 8 MHz, 32 MHz or for both frequencies. All Modules must be nominally functional at 8 MHz, including correct reading of the ID ROM.

#### 2.8. IDSel\* [IP Module Identification]

The active low IDSel\* signal is one of four "select" lines driven by the Carrier board to enable the IP Module. This line is used for reading the 32 byte (ID ROM Format I) or 64 byte (ID ROM Format II) ROM that contains the IP Module identification information. The address lines A1..A5 are used to select the ID byte. IP Module identification information contained in the ROM permits software to perform autoconfiguration.

IDSel\* is unique to each IP Module and is not bussed. All IP Modules must respond to IDSel\*. The configuration ROM contains three classes of information: (i) fixed identification data defined by this Specification, (ii) IP Module dependent data, defined for each IP Module and set by the manufacturer, and (iii) remaining space may be used by the customer, if desired. See Section "ID ROM Data" for more information.

Double-size IP Modules need to have an ID ROM on only their "A" side.

#### 2.9. R/W\* [Data Direction]

The R/W\* signal is driven by the Carrier board to indicate the direction of data flow on the data lines. High indicates a Read cycle (IP Module drives data lines). Low indicates a Write cycle (Carrier board drives data lines). R/W\* may change asynchronously during idle cycles. It must, however, meet the synchronous timing requirements during all select, wait and hold cycles.

R/W\* has the same directional meaning for the data bus for standard cycles and for DMA cycles. It is possible to support a cycle where one IP Module is writing data to another IP Module during the same cycle; however to do this the R/W\* line to each IP Module must be driven separately, and not bussed. Typically, IP Modules read and write data to the host Carrier board only.

#### 2.10. Ack\* [Data Acknowledge]

Ack\* is asserted by the IP Module to terminate each data transfer. Each IP Module may continuously drive Ack\* high or low, or it may tri-state this signal when de-asserted to save power. The minimum data transfer takes two clock cycles (one for the select, one for the acknowledge). This permits a maximum continuous data rate of eight MB/second for each module. Ack\* is driven relative to the rising edge of CLK. See Figure 9 for timing details.

An IP Module may hold off asserting Ack\*, effecting "wait states." The Carrier board may hold a select line asserted on read or write cycles, creating "hold states." After the IP Module asserts Ack\* during hold states, the IP Module then holds Ack\* asserted as a "hold acknowledgment."

Ack\* is not bussed.

There is no fixed maximum amount of time by which an IP Module must assert Ack\*. However the individual IP Module's specification must clearly state access time, or "wait states." In some cases the number of wait states may be a function of external events. If there is a chance that data could be lost then the IP Module must have a maximum wait time. If no Ack\* occurs within this time, then the IP Module will never Ack\*. This permits timeout logic elsewhere in the system to take effect, permitting software to execute a re-try, or otherwise take specific action.

OBSERVATION 2-1: Without this limit, it might be possible for the system timeout and the IP Module's Ack\* to occur simultaneously, losing that data.

#### **2.11.** BS0\*..BS1\* [Byte Select]

The two byte select lines are used to indicate which of the two data bytes are valid. While IP Modules may ignore the byte select lines for some cycles, Carrier boards must drive BS0\* and BS1\* valid on all cycles. IP Modules must observe the byte select lines if they implement 16-bit memory. BS0\* selects the low, or odd, byte (D0..D7). BS1\* selects the high, or even, byte (D8..D15). Both strobes together select both bytes.

The two byte strobes may change asynchronously during idle cycles. They must however meet the synchronous timing requirements during all select, wait and hold cycles.

OBSERVATION 2-2: Big endian byte ordering (Motorola 68K and VMEbus convention) is compatible with IP Modules. This is the convention used throughout this document. Big endian uses even byte addresses (e.g. 0) for the high byte (D8..D15). Carrier boards and software must be careful to document how they map byte addresses. Generally speaking: (1) word addresses for 16-bit devices are even numbered; (2) 8-bit devices are on odd addresses (big endian byte ordering), (3) machines that implement 32-bit busses with no dynamic sizing (e.g. NuBus) will typically map 8-bit IP Modules to every fourth byte address and 16-bit IP Modules in every other word.

OBSERVATION 2-3: Little endian byte ordering (Intel x86 family convention) is compatible with IP Modules, although this convention is not used in the document. Little endian uses even byte addresses (e.g. 0) for the low byte (D0..D7). Carrier boards in little endian systems should always map data lines from the host bus or processor to like numbered data lines on the IP Module, e.g. D0 to D0. Data strobes must be driven appropriate for the actual byte lane(s) used. Carrier boards and software must be careful to document how they map byte addresses. Generally speaking: (1) word addresses for 16-bit devices will not change; (2) 8-bit Modules on odd addresses (using big endian convention) will change to even addresses (under little endian byte ordering).

#### 2.12. IntReq0\*..IntReq1\* [Interrupt Request]

The IP Module specification permits each module two dedicated interrupts. IntReq0\* and IntReq1\* are not bussed. These signals, if used, may by be driven by the IP Module either open drain or by conventional (two state) MOS or CMOS components. Synchronization to CLK is not required by the IP Module. This lack of clock synchronization generally permits standard VLSI components on the IP Module to have their interrupt request outputs directly wired to the connector pins. The Carrier board must provide passive pullup resistors on these signals. The Carrier board may provide synchronization to the clock, if synchronization is required by the Carrier board's interrupt logic.

Reset\* forces any pending interrupt requests to be removed, and interrupts to be disabled until explicitly re-enabled by software. This means that all IP Modules, must provide a way to prevent external signals from generating an interrupt until some access to the IP Module from the host occurs. Ideally there is a control register bit that enables IP Module interrupts.

#### 2.13. DMAReq0\*..DMAReq1\* [DMA Request]

The IP Module specification permits each module two dedicated DMA channels. DMAReq0\* and DMAReq1\* are not bussed. These signals, if used, are driven by the IP Module as conventional (two state) logic to indicate that the IP Module wishes to have a DMA cycle performed. These signals are synchronized to CLK by the IP Module. Carrier boards must have passive pull-ups on these signals to support IP Modules that have no DMA.

See DMA section for more detail.

DMAReqx\* is removed by the IP Module, if there is not an additional DMA request pending, by the falling (asserted) edge of the Ack\* signal driven by the IP Module at the end of the DMA acknowledge cycle. Thus the Carrier board can sample a valid DMAReqx\* on the same clock edge that it finds Ack\* to be valid. An IP Module may delay generating Ack\* with wait states in order to be sure to have DMAReqx\* again valid by this time. Or it may automatically remove DMAReqx\* each cycle, then reassert as soon as it can determine that an additional request is pending.

The DMAReqx\* lines request a compelled I/O DMA cycle. They are not be used to request a DMA cycle to memory on the module.

When the Module requests a DMA cycle, it cannot directly indicate data width nor data direction desired. This information must have been decided in advance of the request.

An IP Module may not request a DMA cycle until such action has specifically been enabled on the Module by the host processor following Reset.

Normally an IP Module would not rescind DMAReqx\* once it is asserted. DMAReqx\* may be rescinded, however, under the following two conditions: (i) a Module no longer is requesting service, due to a change in local conditions, such as an externally caused local reset; and (ii) when it receives a DMAEnd\* input during a zero-wait state DMA Acknowledge cycle during which it is asserting DMAReqx\*. In the latter case, DMAReqx\* should be removed immediately, synchronous to the CLK. In the former case it is possible that a DMA Acknowledge cycle has been committed to by the Carrier board and will occur even without a concurrent DMAReqx\*. This is called a stale DMA Acknowledge cycle. In such a case, the IP Module should be able to handle this cycle. In the latter case, since the Carrier's DMA controller must be reprogrammed (following

its assertion of DMAEnd\*) prior to recognizing DMAReqx\* signals, it will not generate a stale DMA Acknowledge cycle.

#### 2.14. DMAck\* [DMA Acknowledge]

The IP Module Specification supports two types of DMA cycles, I/O DMA and Memory DMA. In both cases the DMA cycle is a modification of the standard I/O or standard Memory cycle. The signal DMAck\* is driven by the Carrier board to indicate that the cycle is a DMA cycle. This signal is timed the same as the A1..A6 Address Bus that is driven at the same time.

I/O DMA cycles are compelled. They occur only in response to the IP Module requesting such a cycle by asserting DMAReq0\* or DMAReq1\*. The Carrier board drives IOSel\*, DMAck\* and A1 low or high to respond. For each I/O DMA cycle there is a previous, corresponding DMA request. A1 is driven low in response to DMAReq0\*, and high in response to DMAReq1\*.

Memory DMA cycles are not compelled. They are similar to standard memory access cycles. The address lines are defined the same as for standard memory cycles. Memory DMA cycles do not occur in response to DMAReqx\*. An IP Module will typically chose to interpret Memory DMA cycles in the same way as it interprets standard Memory cycles. The Carrier board will generally drive the DMAck\* line on DMA Memory cycles when the cycle has been initiated by a DMA controller, rather than the host processor.

OBSERVATION 2-4: DMAck\* is not really an "acknowledge" signal when used with Memory DMA cycles, since it is not in response to a DMA request. It serves primarily in this case to identify to the IP Module that the source of the cycle is a DMA controller. Modules may use this information to process the cycle differently than a standard memory cycle, if that is appropriate to the function of the Module. In this case, the DMAck\* signal may be viewed as a "select modifier."

All DMA cycles may be either reads or writes. The  $R/W^*$  indicates data bus direction in the same way as for non-DMA cycles. DMA cycles may be 8-, 16- or (on double-size Modules) 32-bits wide.

#### 2.15. DMAEnd\* [DMA Termination]

This bidirectional, open-drain line is used to terminate I/O DMA transfers. Both IP Modules and Carriers that support DMA must recognize DMAEnd\* as an input. IP Modules that support DMA may optionally drive DMAEnd\* as an output. Carrier boards that support DMA are recommended to drive DMAEnd\*. DMAEnd\* is driven open-drain by both the Carrier board and the IP Module.

DMAEnd\* may be bussed or non-bussed.

If the transfer ends because a terminal count has been reached the DMA controller on the Carrier normally asserts DMAEnd\*. An IP Module asserting this open drain signal forces DMA termination. The Carrier board and/or the IP Module may assert DMAEnd\* to indicate either abnormal termination or normal termination of the DMA transfers. No additional transfers for that DMA channel should occur, nor any DMA requests for that channel should occur, until the host software has recognized the termination and appropriately responded.

OBSERVATION 2-5: The purpose of DMAEnd\* is to assure that the DMA elements of Modules and Carrier boards stay synchronized relative to DMA "in progress" status. The source of the DMAEnd\* signal (either the Carrier board's DMA controller or the IP Module) would typically generate an interrupt to the host. If DMAEnd\* is used to indicate a premature termination of a transfer then both ends

of the transfer are able to take immediate, appropriate action. If DMAEnd\* is used to signal a normal termination (for example, DMAEnd\* occurring simultaneously with a previously programmed terminal count) then chained DMA, or perhaps continuing normal operation on a communications channel can occur automatically without fear that an error might be lost or overrun in the system.

DMAEnd\* is driven during with the final DMA cycle. The Carrier board asserts DMAEnd\* during the clock cycle following the Select cycle. If there are no Hold states or Wait states then this would be during the Acknowledge state. If there are Wait states then DMAEnd\* would be asserted by the Carrier board prior to the Acknowledge state.

The IP Module asserts DMAEnd\* so that it is valid during its Acknowledge state. It is thus timed similar to valid read data.

OBSERVATION 2-6: If an IP Module needs to know if the Carrier is asserting DMAEnd\*, even if the Module itself is asserting DMAEnd\*, then it may insert at least one Wait state and sample DMAEnd\* during this Wait state, prior to asserting DMAEnd\* itself.

RECOMMENDATION 2-7: IP Modules, particularly at 32 MHz, should not sample DMAEnd\* until the cycle following Select in order that the signal has sufficient time to rise to a valid logic high, since it might have been driven low during the previous cycle.

Both Carrier boards that support DMA and IP Modules that support DMA must have a 1.2 K pullup resistor to +5 volts on this signal line. Modules that do not support DMA should not connect to this signal line. DMAEnd\* must be driven by a 24 mA minimum sink current driver.

#### 2.16. Error\* [IP Module Error]

An IP Module may assert this open-drain signal asynchronously to signal a non-recoverable error. This signal may not be used to indicate invalid bus protocol, time out, nor as a pre-initialization indicator. It may be used to indicate component failure, unrecoverable self-test failures, or serious, hard-wired configuration errors.

Less serious errors should be signaled using an interrupt.

#### 2.17. Strobe\* [Function Strobe]

This uncommitted line may be used as an optional input to or output from an IP Module. It is reserved for a digital strobe or clock signal related to the Module's functionality. For example, Strobe\* could be used for a sample clock to an A/D converter from a local timer, or a communication line clock signal.

Neither Carrier boards nor Modules are required to use the Strobe\* line. Modules that can optionally drive the Strobe\* line must provide a mechanism to disable the Strobe\* driver.

OBSERVATION 2-8: The Strobe\* line may be used for signals that are time critical. Such signals would not be able to use interrupts or other defined communication mechanisms between the Carrier and the Module.

OBSERVATION 2-9: The Strobe\* line may be used for two Modules to communicate with each other without using their I/O wiring or the other defined Module to Carrier communication mechanisms. Such use is beyond the scope of this Specification, however.

RECOMMENDATION 2-10: Carrier boards could provide a passive pullup resistor on the Strobe\* lines, and a simple shunt block that would permit end customers to connect the Strobe\* line of one IP Module to another Module, if desired, via a shunt.

RECOMMENDATION 2-11: IP Modules that use the Strobe\* line should provide the option of implementing the same functionality via an I/O line. This provides compatibility with Carriers that do not connect to the Strobe\* line, and provides a way to communicate with Modules not mounted on the same Carrier.

#### 2.18. GND [Ground]

Four pins are assigned in the four corners of the logic connector for ground. This is the zero volt reference for the logic signals on this connector, and the return path for the power supplies for both digital and analog functions on the IP Modules (that are powered through the logic connector).

Minimum electrical noise in the ground is desirable. This increases noise immunity on digital signals, improves the accuracy of analog functions, and minimizes radiated RF emissions. This specification encourages ground plane construction within both Carrier boards and IP Modules.

External power supplies may be connected to IP Modules via the I/O connector. A Carrier board may provide power to the IP Module logic connector either by wiring it directly from the host machine, regulating or filtering the host supply, connecting to external power or on-board batteries, or other techniques.

OBSERVATION 2-12: System grounding of power supplies, sensors, and external cabling is beyond the scope of this specification. Significant care should be exercised by hardware manufacturers, system integrators, and end users to meet applicable safety and performance requirements.

This is the primary supply for digital logic functions on the IP Module. Two pins provide for up to two Amperes of current maximum from this supply.

OBSERVATION 2-13: Power supply regulation, conducted RF noise, and power dissipation are beyond the scope of this specification. However good regulation and the use of RF filtering is a recommended practice. Similarly, power dissipation on IP Modules should be kept to a minimum.

Please see additional discussion under GND, above.

These two power supplies are primarily used to power analog and communication functions on IP Modules. One pin is available for each voltage, providing a maximum current of 1 Ampere each.

OBSERVATION 2-14: Power supply regulation, conducted RF noise, and power dissipation are beyond the scope of this Specification. However good regulation and the use of RF filtering is a recommended practice. Similarly, power dissipation on IP Modules should be kept to a minimum.

These two power supplies are not required to be supplied by the Carrier boards, but are strongly recommended. Carrier boards that do not provide these voltages must be clearly marked.

IP Modules that require these, or other voltages, may chose to have them provided (required or optionally) via the I/O connector.

Please see additional discussion under GND.

#### 2.21. Reserved

These two pins may be used in future revisions to support additional features. Carrier boards should connect to these pins with passive pull-up resistors.

## 3. Cycle Types

The following table shows allowable data transfer cycle types and their implementation using the Carrier board driven control signals. This table is for single-size (16-bit) Modules. See Section 32-bit Operation for more information on double-size 32-bit cycle types.

Cycle Type R/W\* IOSel\* MemSel\* IntSel\* IDSel\* DMAck\* Η L Η Η Η Η Input Output L L Η Η Η Η **Memory Read** Н L Н Н Η Η **Memory Write** L Η L Η Η Η **Interrupt Ack** Η Η Η L Η Η Η Н Н Η L Η ID Read Η Η Η I/O DMA Read Η L L L Η L I/O DMA Write L Η Η Н Memory DMA Rd Η L Η Η L L Memory DMA Wr L Η Η Н L

**Table 2** Cycle Types

Note that exactly one of the four IP Module select lines (IOSel\*, MemSel\*, IntSel\* or IDSel\*, shown in bold) is asserted for each cycle type.

The following table shows allowable memory addressing by cycle type. This table is for single-size (16-bit) Modules. See Section 32-bit Operation for more information on addressing on double-size 32-bit Modules.

| Cycle Type    | Address Space (size) | Address Lines Used |

|---------------|----------------------|--------------------|

| Input         | 64 words             | A1A6               |

| Output        | 64 words             | A1A6               |

| Memory Read   | Up to 8 Mbytes       | A1A22 Note 1       |

| Memory Write  | Up to 8 Mbytes       | A1A22 Note 2       |

| Interrupt Ack | 2 vectors            | A1                 |

| ID Read       | 32 or 64 bytes       | A1A5 Note 3        |

| I/O DMA       | 2 channels           | A1 Note 4          |

| Memory DMA    | Up to 8 Mbytes       | A122               |

**Table 3** Address Spaces by Cycle Type

Note 1: Byte memory reads are supported by the Carrier board: the IP Modules always read either eight or 16 bits wide fixed.

Note 2: Memory write cycles use BS0\* and BS1\* to select the lower byte, upper byte or word (16 bit) access. The minimum and maximum address spaces for memory read cycles and write cycles is the same.

Note 3: Format I ID reads are on the lower, byte (D0..D7). Format II ID reads are 16-bits wide.

Note 4: I/O DMA cycles use A1 to indicate which channel is being acknowledged.

## 4. Addressing Conventions

#### **4.1. A0 Usage**

The IP Module Logic Interface does not use A0. A0 as used by the host is normally used to select the high or low 8-bit byte out of a 16-bit word. Traditionally A0 is the least significant address line that can address individual bytes. (This is no longer true on all processors, such as DSPs.) The Logic Interface uses a 16-bit data bus. 16-bit wide memory (RAM) uses the byte selects for byte writes to fully support eight and 16 bit memory operations from the host and/or DMA.

Address notation follows the industry convention. This is sometimes called "byte addressing." A0 is thus implicitly present in all written addresses.

This Specification uses the convention that the low order byte in a word is called address one, or "odd." Byte-wide I/O addresses are normally on the low order byte, thus occupy consecutive odd addresses. This is consistent with "big endian" architectures, such as the Motorola 68K family and the VMEbus. IP Modules are also compatible with little endian systems.

See discussion under I/O Space and Memory Space, and under the BSx\* lines, for more details.

#### 4.2. Words versus Bytes

This specification uses the convention that data width for registers is fixed in the design of the Module. These registers are typically accessed in the I/O Space. Accesses within the Module's Memory Space are assumed to access memory, and that both byte and word addressing is supported. These conventions are not fixed requirements of this specification, however. Modules may support flexible register data width, although this is rare. Modules may also support fixed memory data width, although this is not recommended.

A more common situation is the placing of registers in the memory space. In this case, access width may be fixed, even though access in the memory space. This occurs, for example, when an IC has more than 64 registers, or an IC provides fixed address register decoding in an address space that is larger than 64 words. Another case of fixed data width in the memory space can occur when a Module uses registers suitable for high-speed DMA (for example FIFO data registers), but wishes to make them available for non-compelled DMA access.

## 5. I/O Space

The six address lines give  $2^6$  or 64 I/O locations. Each location may be 16 bits wide. In many cases only eight bits will be used. When only eight bits are used they must be the low order (D0..D7). It is not necessary that all of the bits read or written (8 or 16) be meaningful, but it is necessary to drive either eight or 16 of the data lines.

A peak continuous rate of 64 MB/sec (two clocks per cycle) is available for 32-bit, 32 MHz I/O writes and I/O DMA write cycles. A peak continuous rate of 42.67 MB/sec (three clocks per cycle) is available for 32-bit, 32 MHz I/O reads and I/O DMA read cycles.

Passive pullup resistors on the Carrier board guarantee that undriven lines are always read as a logical one.

Each IP Module should verify that only the IOSel\* is asserted each cycle, to avoid confusion with any future definitions of advanced cycle types that might be implemented by asserting multiple select lines.

Each IP Module uses 128 bytes out of the I/O space of the host. Some Carrier boards use A7 to decode the ID ROM space of each IP Module. In this case each IP Module uses 256 bytes out of the host's I/O space. This permits 256 IP Modules in one 64 KB I/O space.

OBSERVATION 5-15: NuBus and some other busses are 32-bits wide only. One likely mapping is that each IP Module occupies the low 16 (or 8) bits out of each 32-bit long word. Carrier boards on these busses that use this mapping must make this explicit in all documentation. Address maps given for IP Modules may be converted to NuBus addresses by multiplying the IP Module address by two and adding two.

OBSERVATION 5-16: This specification does not enforce any particular mapping by Carrier boards between the host(s) and the IP Module(s). Busses and processors 64 bits wide, for example, may use unconventional mappings. These unconventional mappings may not be software compatible across different systems, however.

## 6. Memory Space

The IP Module format permits IP Modules to contain substantial memory. The fully synchronous data transfer cycles make it easy to multiplex the data bus with the high order 16 address lines. The minimum data transfer cycle is two clocks, permitting a maximum continuous data transfer rate of basic IP Modules (8 MHz, 16-bit access) of eight MB/sec. 32-bit, 32 MHz Modules will support a peak memory write rate of 42.67 MB/sec (three clocks per cycle), and a peak memory read rate of 32 MB/sec (four clocks per cycle). A peak rate of 64 MB/sec is available for 32-bit, 32 MHz I/O writes and I/O DMA write cycles.

An IP Module may have only memory, only I/O, or both memory and I/O. During memory cycles the first clock cycle is used to transmit the memory address on the data lines. The second clock cycle is then used to move eight or 16 bits of data. More clock cycles may be used if needed by the IP Module by not asserting Ack\* until it is ready to terminate the cycle.

The dedicated six low address lines plus the 16 address lines that share the data bus produce a maximum address space of  $2^{22}$  words or eight MB per module. Unlike the 64 words of I/O space, each memory IP Module takes a variable amount of memory. Different Carrier boards implement memory addressing differently. Memory data width may be either eight or 16 bits, although 16 bits is more common. Details of the memory (size, type, speed, width) are contained in the configuration ROM on each IP Module. This permits software to perform autoconfigurations, as well as automatic memory diagnostics on power up.

Each IP Module should verify that only the MemSel\* is asserted each cycle, to avoid confusion with any future definitions of advanced cycle types that might be implemented by asserting multiple select lines.

OBSERVATION 6-17: NuBus and some other busses are 32-bits wide only. One possible mapping is that each IP Module occupies the low 16 (or 8) bits out of each 32-bit long word. This mapping may be inappropriate for some types of memory. Note however that this mapping is common on NuBus, even for code (which is copied into contiguous memory prior to being executed.) Carrier boards on these busses that use this mapping must make this explicit in all documentation. Address maps given for IP Modules may be converted to NuBus addresses by multiplying the IP Module address by two and adding two.

OBSERVATION 6-18: This specification does not enforce any particular mapping by Carrier boards between the host(s) and the IP Module(s). Busses and processors 64 bits wide, for example, may use unconventional mappings. These unconventional mappings may not be software compatible across different systems, however.

## 7. Direct Memory Access

#### 7.1. I/O DMA Cycles

Direct memory access (DMA) control is handled primarily by circuitry on the Carrier board. DMA features may be optionally supported by IP Modules and Carrier boards. For DMA cycles to occur both the Carrier and IP Module must support DMA.

DMA cycles are available in two types: I/O DMA and Memory DMA. Only the I/O DMA is compelled via a DMA request from the IP Module.

Prior to any I/O DMA cycles occurring, the host software must program the Carrier-based DMA controller and enable DMA on the IP Module. Reset\* will halt any DMA activity until both the Carrier board and the IP Module are programmed by the host software. An IP Module initiates DMA activity by asserting one of its two DMAReqx\* lines low, synchronous to the IP Module CLK. The DMA controller on the Carrier board responds by generating a DMA acknowledge cycle, which is a modification of a standard I/O data transfer cycle. The IP Module removes the DMA request line prior to the end of the cycle, unless it has another request ready, in which case it may leave the request line asserted.

DMA cycles may effectively be throttled by either the IP Module or the DMA controller on the Carrier board. If the IP Module does not wish to have another DMA cycle occur yet, it simply does not reassert its request line. If the DMA controller wishes to postpone the DMA cycle (perhaps because it is allocating bus bandwidth among competing requesters) it simply delays generating the DMA acknowledge cycle.

Either the IP Module or the Carrier board's DMA controller may drive DMAEnd\*. The DMA controller would typically drive DMAEnd\* when either a terminal count was reached or there was an error condition that prevents further DMA cycles from being effective (such as a host memory error or bus error). The IP Module would typically drive DMAEnd\* when it recognized a logical end of data (as might happen with variable length data communication packets) or when it encountered an error condition (for example a SCSI error in the middle of a sector). When DMAEnd\* is asserted the host is interrupted and must interpret the cause of the termination and take appropriate action. IP Modules that support DMA must recognize DMAEnd\*. Carrier boards that support DMA must recognize DMAEnd\* applies only to the channel being accessed in that cycle.

Note that a Carrier board's DMA controller, when recognizing DMAEnd\*, may not need to be explicitly reprogrammed by the host processor if it has the ability to respond appropriately internally. For example, the DMA controller may support "chained" DMA operations, or it may have its own internal processor.

There are two DMA channels per single-size IP Module. There are four channels on a double-size IP Module. The request lines are non-multiplexed: DMAReq0\* and DMAReq1\* for the channel 0 and channel 1 respectively. The acknowledge cycle encodes the DMA channel number into A1. For 32-bit DMA, the request lines should be from the A side of the double-size Module.

I/O DMA cycles are a modification of standard I/O cycles. DMAck\* is driven, similarly to an address line (A1..A6 timing), while IOSel\* is asserted during the Select state. A1 is the only address line driven valid. A1 low indicates the cycle is responding to DMA request channel 0 (DMAReq0\*) while A1 high indicates the cycle is responding to DMA request channel 1 (DMAReq1\*). IP Modules should ignore address lines A2..A6 during DMA cycles. I/O-DMA cycles have the same data width options, eight through

32 bits, as standard I/O cycles. Unless otherwise stated, the cycle has similar characteristics to standard I/O cycles.

Because DMAReqx\* is valid when Ack\* is asserted (on the same rising CLK edge) it is possible to implement "back-to-back" DMA cycles.

See Section 18 for permissible combinations of DMA support.

#### 7.2. Memory DMA Cycles

Memory DMA cycles are very similar to regular Memory cycles.

A variation on standard memory cycles is called a Memory DMA cycle. Unlike standard I/O DMA cycles, the address lines are used as in a standard Memory cycle. A1 is a memory address line; it is not used to indicate a DMA channel. Indeed, since the DMA Request lines are used only for requesting I/O DMA channels, there are no identifiable "Memory DMA" channels.

On Memory DMA cycles, the Carrier drives DMAck\* true along with MemSel\*. Timing for DMAck\* is similar to an address line A1..A6. DMAEnd\* may be driven by either the IP Module or the Carrier Board to indicate the last Memory DMA cycle. Note that the function of DMAEnd\* on Memory DMA cycles is somewhat different than for I/O DMA cycles, since there are no associated DMA requests across the IP Module interface. Data width and other characteristics are the same as for standard Memory cycles.

See Section 18 for permissible combinations of DMA support.

## 8. Interrupt Acknowledge

When an IP Module needs service it asynchronously asserts IntReq0\* or IntReq1\*, either open-drain or with a standard driver. These signals are not bussed.

The Carrier board responds by doing an interrupt acknowledge cycle. The select line IntSel\* is asserted along with A1. A1 low responds to IntReq0\*. A1 high responds to IntReq1\*. The IP Module places its vector as valid data on the data lines (8-bit vectors use the low data lines D0..D7) and asserts Ack\*. The interrupt request signal is removed either during the interrupt acknowledge cycle or later, when the IP Module has been serviced by a software routine.

IP Modules that have only a single interrupt should use IntReq0\*.

Neither Modules nor Carrier boards are required to support interrupts. Interrupt support is strongly recommended.

### 9. ID ROM Data

The ID ROM has previously been called the "ID PROM." This is "read-only-memory" in the sense that under normal operation the user would not be able to change this configuration memory. Although not necessarily "programmable" in the traditional usage of this term, this Specification does not specify the the method or technology the manufacturer of the IP may use to create the ID ROM.

There are two basic permissible formats for the required ID ROM on all IP Modules. The first format, Format I, dates back to the earliest modules, uses an 8-bit wide data path and 8-bit Manufacturer ID field.

Format II is newer. It uses 16-bit wide data and a 24 bit Manufacturer ID field.

Each IP Module must contain a configuration ID ROM whose size is at least 12 x 8. This ID ROM is read by the IDSel\* line, and address lines A1 through A5. Type I ID ROM data is placed on the low order, D0..D7 data lines. Type II data is place on all 16 data lines. Double-size IP Modules need only have an ID ROM on the A side. Data is read when R/W\* is high and IDSel\* is asserted. A6 should be low during ID ROM reads.

The ID ROM contains three classes of information:

- Fixed identification data in one of two formats,

- IP Module dependent data, defined for each Module type and set by the manufacturer.

- Remaining space may be used by a system integrator or end user, if the ROM data is accessible to them on the Module.

Data formats are shown in the two Tables below.

RECOMMENDATION 9-19: Write cycles into the ID space are undefined by this Specification. It is recommended that Carrier boards provide the capability to write into the ID space. Read cycles to addresses where A6 is high are undefined by this Specification. It is recommended that Carrier boards provide the capability to access this portion of the ID space.

OBSERVATION 9-20: Data in the ID ROM space may be provided by a dedicated ROM component, or by logic in an FPLD or other means.

ID ROM access must take less time than 4.0 µsec, once the IP Module is initialized.

OBSERVATION 9-21: Note that some IP Modules take many milliseconds to initialize following Reset (for example, loading Xilinx® devices). Host systems should be able to tolerate a long delay following Reset prior to reading IP Module's ID ROMs. IP Module manufacturers must state the longest time required following the end of Reset prior to functionality.

#### 9.1. ID ROM Data Format I

Table 4 ID ROM Data Format I

| Address | Description              | Contents |

|---------|--------------------------|----------|

| 3F      | User Space               |          |

| 2*nn+1  |                          |          |

| 2*nn-1  | IP Module Specific Space |          |

| 19      |                          |          |

| 17      | CRC                      |          |

| 15      | Number of bytes used     | =nn      |

| 13      | Driver ID, high byte     |          |

| 11      | Driver ID, low byte      |          |

| 0F      | Reserved                 | 00       |

| 0D      | Revision                 |          |

| 0B      | Model Number             |          |

| 09      | Manufacturer ID          |          |

| 07      | ASCII "C" or ASCII "H"   | 43 or 48 |

| 05      | ASCII "A"                | 41       |

| 03      | ASCII "P"                | 50       |

| 01      | ASCII "I"                | 49       |

The fixed data space contains twelve bytes.

The low four bytes contain the ASCII text "IPAC" for 8 MHz or "IPAH." "IPAC" is used for 8 MHz only design; "IPAH" is used on Modules that run at 32 MHz. These four ASCII bytes at the base of the ID space identify the Module as installed, and containing a Format I ID ROM.

Table 4 assumes big endian byte ordering. Thus the consecutive bytes of the ID ROM are on the low byte of the data bus and occupy consecutive ODD byte addresses. Other architectures—while fully compatible with IP Modules—may use a different host addressing scheme. For example little endian architecture machines will place these bytes locations on consecutive EVEN byte addresses. Some 32-bit NuBus implementations, for example, might place these bytes on every fourth byte addresss.

Byte 09 of Format I is the Manufacturer ID. Up until this Specification is approved by VSO, these numbers are assigned by GreenSpring Computers, Inc, at no charge. Requests should be made in writing, delivered via mail or fax, and include:

- Contact Name

- Company name and address

- Phone and fax

- Indication if product(s) are for internal use only or will be sold on the open market

- Indication if the products are Modules or Carrier boards.

- Optionally, a short description of the product may be included.

GreenSpring may be contacted at:

GreenSpring Computers, Inc. 1204 O'Brien Drive Menlo Park CA 94025 voice: 415.327.1200 fax: 415.327.3808

When this Specification is approved by the VSO, the VSO or its designate shall assign Manufacturer ID numbers. For contacting VSO, see the front of this document.

8-bit Manufacturer ID numbers FF and 00 are never used. Numbers in the range 01 to 0F may be used by anyone as "unregistered" or for prototype IP Modules.

The next two bytes, Model Number and Revision, are set by the manufacturer. Byte 0F is reserved for future extension. It is set to 00.

RECOMMENDATION 9-22: Interpretation of the Revision field is up to each individual manufacturer. A recommended format is to start with (hexadecimal) \$A1. The first hex letter increments for major product revisions that impact the product's specifications or performance. The digit increments for minor revisions.

OBSERVATION 9-23: The Revision field could be used by systems integrators for configuration management. By comparing against a minimum revision level or a known fixed revision it is possible for the system software to assure that only compatible Modules will be installed during maintenance or system upgrades.

The next two bytes contain a sixteen bit field reserved to identify an appropriate software driver. The number 0000 means no driver is specified. The interpretation of this field is beyond the scope of this Specification.

The byte at address \$15 in Table 4 contains the number of bytes used in the ID ROM for fixed data and IP Module specific data. If no IP Module specific data is used then this number is (hex) \$0C, for the (decimal) twelve bytes of fixed data. The first byte in the ID ROM that is free for user data is at address 2\*nn+1, where nn is the number in the byte at address 15. There is no requirement that any user space be provided.

An 8-bit CRC checksum is used in byte \$17 to verify that the information in the ID ROM is being read correctly. This CRC covers only the number of bytes set by the manufacturer: this number is at address \$15 (discussed in the previous paragraph). The CRC used is an industry standard. It is the low eight bits of the FCS as described in CCITT T.30 (Fascicle VII.3) section 5.3.7. Byte \$17 is first set to zero for the generation of the CRC.

Sample programs to generate and check the CRC may be found in the Appendix to this Specification. These programs are not validated and are provided as examples only.

## 9.2. ID ROM Data Format II

Table 5 ID ROM Data Format II

| Address | Description                           | Contents     |

|---------|---------------------------------------|--------------|

| 3E      | User Space                            |              |

| nn+2    |                                       |              |

| nn      | IP Module Specific Space              |              |

| 20      |                                       |              |

| 18      | 16-bit CRC                            |              |

| 16      | Number of bytes used, 16-bit quantity | = nn         |

| 14      | 16-bit Flags                          |              |

| 12      | Reserved for Driver ID, high word     |              |

| 10      | Reserved for Driver ID, low word      |              |

| 0E      | Reserved                              | 0000         |

| 0C      | Revision, 2 bytes                     |              |

| 0A      | Model Number, 2 bytes                 |              |

| 08      | Manufacturer ID, low 16 bits of 24    | уууу         |

| 06      | Manufacturer ID, high 8 bits of 24    | <b>00</b> yy |

| 04      | ASCII "4 <space>"</space>             | 3420         |

| 02      | ASCII "TA"                            | 5441         |

| 00      | ASCII "VI"                            | 5649         |

The fixed data space contains thirteen 16-bit words.

The low three words contain the ASCII text "VITA4 ." Note that the "V" is in the high byte; the "I" is in the low byte. These six ASCII characters at the base of the ID space identify the Module as installed, and containing a Format II ID ROM.

The two words at addresses 06 and 08 contain a 24-bit IEEE Manufacturer ID number. The high eight bits in the ID ROM are filled with zero. Note that this Manufacturer ID number is different than the one contained in Type I format ID ROMs. These numbers were originally assigned by IEEE to form part of a 48-bit unique node identifier "MAC address" as specified in IEEE Std 802.3 (ISO/IEC 8802-3) Section 3.2.3. IEEE calls this number an "Organizationally Unique Identifier."

IEEE may be contacted at:

Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street

New York NY 10017-2394

Organizationally Unique Identifiers may be obtained by contacting the IEEE Registration Authority at:

Institute of Electrical and Electronics Engineers, Inc.

Registration Authority, IEEE Standards Department

PO Box 1331

445 Hoes Lane

Piscataway NJ 08855-1331

voice: 908 562 3813

voice: 908.562.3813 fax: 908.562.1571

At the time of this writing, there was a US\$1000 fee for each Organizationally Unique Identifier. See also IEEE Std 802-1990.

The next two words, Model Number and Revision, are defined and set by the manufacturer.

RECOMMENDATION 9-24: Interpretation of the 16-bit Revision field is up to each individual manufacturer. A recommended format is to start with ASCII A1 (hex \$4131). The first ASCII letter increments for major product revisions that impact the product's specifications or performance. The ASCII digit increments for minor revisions.

OBSERVATION 9-25: The Revision field could be used by systems integrators for configuration management. By comparing against a minimum revision level or a known fixed revision it is possible for the system software to assure that only compatible Modules will be installed during maintenance or system upgrades.

The 16-bit reserved field should be set to 0000.

The next two words contain a 32-bit field reserved to identify an appropriate software driver. The number 0000 0000 means no driver is specified. The interpretation of this field is beyond the scope of this Specification.

The next 16-bits are reserved for Flags. The bits are currently defined:

- D0 = 0, identifies this revision of the specification for the ID ROM,

- D1 = 1 for 8 MHz functionality supported, D1 = 0 for 8 MHz operation not recommended.

- D2=1 for 32 MHz functionality supported, D2 = 0 for 32 MHz operation not supported or not recommended.

- Bits D3..D15 must be set to zero.

Note that the ID ROM itself must always be readable at 8 MHz. D1 = 0 means that the manufacturer does not recommend that the Module be operated at 8 MHz for its intended function. D1=1 means that the module is specified at 8 MHz.

A Module may be designed for 8 MHz operation only, or for both 8 and 32 MHz operation, or primarily for 32 MHz operation.

The word at address \$16 in Table 5 contains the number of bytes used in the ID ROM for fixed data and IP Module specific data. If no IP Module specific data is used then this number is (hex) \$1A, for the (decimal) 26 bytes of fixed data, including the CRC. The first word in the ID ROM that is free for user data is at address nn. where nn is the number in the word at address \$16. There is no requirement that any user space be provided.

A 16-bit CRC checksum is used in word \$18 to verify that the information in the ID ROM is being read correctly. This CRC covers only the number of bytes set by the manufacturer: this number is at address \$16 (discussed in the previous paragraph). The CRC used is an industry standard. It is the low 16 bits of the FCS as described in CCITT T.30 (Fascicle VII.3) section 5.3.7. Word \$18 is first set to zero for the generation of the CRC.

Sample programs to generate and check the CRC may be found in the Appendix to this Specification. These programs are not validated and are provided as examples only.

# 10. 8 MHz Data Transfer Cycle Details

This section describes basic cycle operation between the Carrier board and the IP Module. This section applies specifically to 8 MHz operation. See following sections for 32 MHz operation. Since 32 MHz operation is described in this document as a variation on the basic 8 MHz operation, this section is still applicable to 32 MHz operation, with the modifications described in the following sections.

All data transfers are performed synchronously to the 8 MHz CLK. Signals are changed following the rising edge of CLK. Interface signals are typically sampled on the rising edge of CLK.

The IP Module generates signals back to the Carrier board each cycle: Ack\* and, for read cycles, Data. For DMA cycles, the signals DMAReqx\* and DMAEnd\* are also generated valid (asserted or not asserted) each cycle. For interrupts, the signals IntReqx\* are generated by the IP. However these two interrupt requests, unlike all of other signals, may be generated and removed asynchronous to the clock.

The fastest and simplest data transfer cycle uses two clock periods. During the first clock period the Carrier board asserts one of four *select* lines (IOSel\*, MemSel\*, IntSel\*, IDSel\*) and drives the address bus valid. During the second clock period, the IP Module asserts Ack\* to *terminate* the cycle. Data is nominally transferred at the end of this clock period. The basic cycle may be extended by the IP Module by inserting *wait* states between the select and termination clock cycles. On reads, the Carrier board may extend the cycle—causing data from the IP Module to be held valid—by inserting *hold* states. If no cycle is in progress the clock cycles are identified as *idle* states.

Typical data transfer cycles are shown in Figure 2 through Figure 9. The states are identified in smaller type above each clock period.

It is convenient to associate each clock cycle (clock period) with one of five states: select, terminate, wait, hold or idle. These are printed in italics is this section, and are used in the timing and state diagram figures near the end of this Specification.

The two states select and terminate are required for all data transfers. These two states are always one clock cycle long each. Wait, hold and idle states are optional.

See Figure 11, which shows the Data Transfer State Diagram.

The *idle* state is exited when the Carrier board asserts one of the four select lines. The select line may be asserted for as little as one clock cycle.

Any number of wait cycles may be inserted between the select cycle and the terminate cycle by the IP Module by not asserting Ack\*. There is no explicit provision for cycle timeout. Even if an IP Module supports a specific select line it is not required to always assert Ack\* in response to that select line. (If an IP Module is not driving an interrupt request it does not have to respond to IntSel\*, for example.) Conversely, an invalid address to an IP Module does not require that IP Module to fail to assert Ack\*.

There is no fixed maximum amount of time by which an IP Module must assert Ack\*. However the IP Module literature must clearly state access time, or "wait states." In some cases the number of wait states may be a function of external events, in which case a maximum time must be stated.

RECOMMENDATION 10-26: IP Modules' maximum Ack\* time should generally be not be more than a few microseconds.

If a Carrier board wishes to force an IP Module to prematurely terminate a cycle the Carrier board must assert Reset\*.

The Carrier board may extend any read or write cycle by holding the select line asserted. There is no specified maximum number of hold states. If an IP Module requires a limit to the number of hold states in order for it to function properly, it should state that limit in its literature.

RECOMMENDATION 10-27: Hold states should not exceed four microseconds (32 hold states).

The Carrier board does not have to hold data valid on write cycles on any clocks past the *terminate* state. That is, the Carrier board may hold the select line true after Ack\*, for its convenience, introducing hold states. The IP Module acknowledges these hold states by holding Ack\* true; however the internal write cycle on the IP Module has been completed, and so data is ignored.

OBSERVATION 10-28: A single data transfer cycle may have either wait states, or hold states, or both, or neither.

# 11. 32-bit Access

IP Module may be accessed using 32-bit wide data if the IP Module is a double-size.