# Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC

Sponsored by the

Microprocessor & Microcomputer Standards Committee (MMSC)

of the IEEE Computer Society

P1386.1/Draft 2.4

January 12, 2001

Draft submitted to IEEE for final standardization approval

**Abstract:** This draft standard, in conjunction with P1386 (CMC), defines the physical and environmental layers of a PCI Mezzanine Card (PMC) Family to be usable on (but not limited to) single slot VME, VME64 & VME64x boards, CompactPCI Boards, Multibus I boards, Multibus II boards, desktop computers, portable computers, severs and similar types of applications. The electrical and logical layers are based on the PCI Specification from the PCI Special Interest Group. The PCI Mezzanine Cards allow for a variety of optional function expansions for the host system. I/O functionality from the PMC may be either through the mezzanine front panel, or via the backplane by routing the I/O signals through the mezzanine connector to the host.

**Keywords:** Backplane I/O, Bezel, Board, Card, CompactPCI, Face Plate, Front Panel I/O, Metric, Host Computer, I/O, Local Bus, Mezzanine, Module, Modular I/O, PCI, Multibus I, Multibus II, VME, VME64, VME64x, VMEbus.

Copyright (c) 2001 by the Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street

New York, NY 10017, USA

All rights reserved.

This is an unapproved draft of a proposed IEEE Standard, subject to change. Permission is hereby granted for IEEE Standards Committee participants to reproduce this document for purposes of IEEE standardization activities. If this document is to be submitted to ISO or IEC, notification shall be given to the IEEE Copyright Administrator. Permission is also granted for member bodies and technical committees of ISO and IEC to reproduce this document for purposes of developing a national position. Other entities seeking permission to reproduce portions of this document for these or other uses must contact the IEEE Standards Department for the appropriate license. Use of information contained in this unapproved draft is at your own risk.

IEEE Standards Department Copyright and Permissions 445 Hoes Lane, PO Box 1331 Piscataway, NJ 08855-1331, USA IEEE Standards documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within the IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside the IEEE which have expressed an interest in participating in the development of the standard. Use of an IEEE Standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE standard is subjected to review at least once every five years for revision or reaffirmation. When a document is more than five years old, and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of the IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board

445 Hoes Lane

P.O. Box 1331

Piscataway, NJ 08855-1331

USA

IEEE Standards documents are adopted by the Institute of Electrical and Electronic Engineers without regard to whether their adoption may involve patents on articles, material, or processes. Such adoption may not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the standards documents.

#### Comments

If you have questions or comments regarding this draft, please contact the chair/draft editor of this proposed standard:

Wayne Fischer

P1386.1 (PMC) Chair & Draft Editor

Tahoe Embedded Computers

PO Box 8600

Incline Village, NV 89452-8600 USA

Ph: 775-832-0447

Em: tahoewayne@nvbell.net

Ws: www.TahoeWayne.com

# **Change Bars**

All paragraphs changed in this draft (2.4) from draft 2.3 are marked with a change bar on the right side of the paragraph. Any table entry that was changed will have a thicker vertical line on the right side of changed entry.

#### Introduction

(This introduction is not part of this Draft Standard Physical and Environmental Layers for a PCI Mezzanine Card: PMC)

This draft standard provides the specifications for implementing the PCI local bus between a host and mezzanine card based on the P1386 (CMC) Standard for usage on VME64x boards, CompactPCI boards, and Multibus I & II boards. PCI boards defined for the general personal computer market will not fit on these boards since they mount perpendicular on the host computer. This standard provides the necessary mechanical and environmental requirements for the use of PCI based mezzanine cards in a large variety of low profile applications. PCI Mezzanine Cards can provide front bezel I/O, backplane I/O via the host, additional local host functions or a combination of the three.

Special thanks are due to Dave Moore, original P1386.1 Working Group Draft Editor, for the generation of the many drafts, Rick Spratt, Cliff Lupien, Harry Parkinson, Chau Pham and Heinz Horstmeier for their contribution to development of this proposed standard.

At the time this standard was completed, the P1386.1 Working Group had the following membership:

Wayne Fischer, Chair Chau Pham, Vice Chair

Malcom Airst Dave Horton Harry Parkinson Harry Andreas Anotol Kaganovich Elwood Parsons James Barnette Gary Kidwell Chau Pham Tom Kuleza Juergen Baumann Dave Rios Martin Blake Jing Kowk John Rynearson Dees Lambreshtse Hans Brand Richard Spratt Dave Brearley Sang Dae Lee Nobuaki Sugiura Gorky Chin Cliff Lupien Dennis Terry Dick DeBock Kristian Martinson Russ Tuck Ian Dobson Jim Medeiros Jim Turley Wayne Fischer Mark Vorenkarmp Robert McKee Mike Hasenfratz Dave Mendenhall Eike Waltz Ryuji Hayasaka David Moore Dave Wickliff Roger Hinsdale Rob Noffke Bob Widlicka Heinz Horstmeier David Wright Joseph Norris

The following people were on the IEEE sponsor balloting committee: List to be provided,

When the IEEE Standards Board approved this standard on XX Xxxx, 2001, it had the following membership:

List to be provided,

Also included are the following nonvoting IEEE Standard Board liaisons: List to be provided,

# **Contents**

| 1.         |                | view                                                                                    |     |

|------------|----------------|-----------------------------------------------------------------------------------------|-----|

|            |                | Scope                                                                                   |     |

|            |                | Purpose                                                                                 |     |

|            |                | General Arrangement  Dimensions                                                         |     |

|            | 1, 1           | Difficusions                                                                            | _   |

| 2.         |                | ences                                                                                   |     |

|            | 2.1            | Trademarks                                                                              | 3   |

| 3.         | Defin          | itions, Abbreviations and Terminology                                                   | 3   |

|            |                | Special Word Usage                                                                      |     |

|            |                |                                                                                         | _   |

| 4.         |                | anics and Compliance                                                                    |     |

|            |                | Conformance                                                                             |     |

|            |                | PMC Voltage Keying  Connector Configurations                                            |     |

|            |                | Power Consumption, Heat Dissipation and Air Flow                                        |     |

|            |                | Electromagnetic Compatibility                                                           |     |

|            | 4.6            | Shock and Vibration                                                                     |     |

|            |                | Environmental                                                                           |     |

|            |                | MTBF                                                                                    |     |

| _          | Elect.         | rical and Logical Layer                                                                 | _   |

| Э.         |                | Connector Utilization                                                                   |     |

|            |                | PMC Connector Pin Assignment                                                            |     |

|            |                | Comparison of Pin Usage, PCI to PMC                                                     |     |

|            |                | Mapping of PCI Reserve Pins                                                             |     |

|            | ٠              |                                                                                         | . • |

| ъ.         |                |                                                                                         |     |

| F1         | gures          |                                                                                         | 0   |

|            | Figur<br>Figur | J 1                                                                                     |     |

|            |                | re 5-1 Connector Orientation on PMC, Side 1re 5-2 Connector Orientation on Host, Side 1 |     |

|            | rigui          | e 5-2 Connector Orientation on most, side 1                                             | O   |

| <b>~</b> - | 1.1            |                                                                                         |     |

| 1 a        | bles           | T. 1. DMC Commenters Discharing many                                                    | _   |

|            | Table          |                                                                                         |     |

|            | Table<br>Table |                                                                                         |     |

|            | rable          | : J-J FUI-RESELVEU/FING RETATIONSHID                                                    | . U |

# Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC

#### 1. Overview

# 1.1 Scope

This draft standard defines a family of slim modular mezzanine cards for VME, VME64 VME64x, CompactPCI, Multibus I & II, desktop computers, portable computers, servers and other computer systems with the logical and electrical layers based on the PCI (Peripheral Component Interface) Specification from the PCI Special Interest Group.

The complete physical (mechanical) and the environmental layers are specified within the Common Mezzanine Card (CMC) Standard P1386 [1]<sup>1</sup>.

## 1.2 Purpose

PCI is a high speed local bus being used by a variety of microprocessors. The PCI specification defines multiple board sizes that plug into computer mother boards in a perpendicular fashion. These perpendicular boards are not usable for low profile computer applications. This draft standard defines the mechanics of a slim, modular, parallel mezzanine card family that uses the logical and electrical layers of the PCI specification for the local bus. I/O can be via the front bezel and/or through the connector to the host computer for backplane I/O. Additional local functionality can also be provided by these mezzanine cards.

# 1.3 General Arrangement

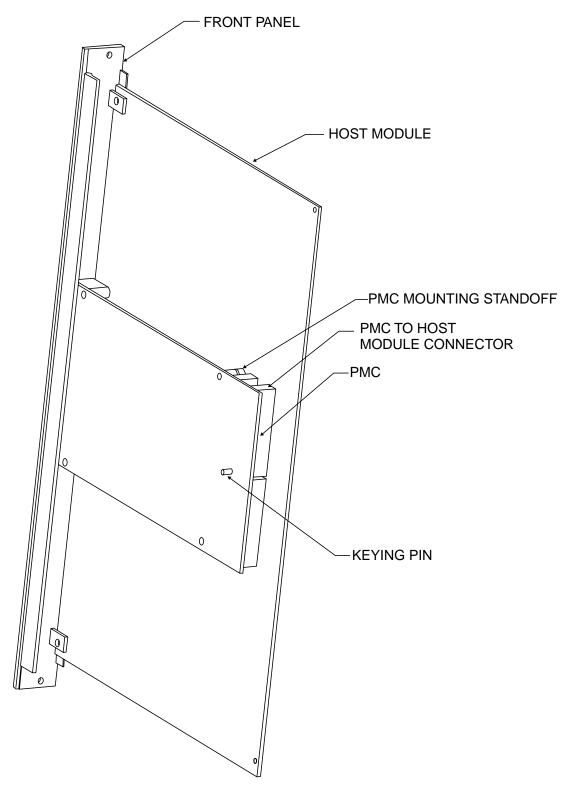

PCI Mezzanine Cards (PMC) are intended to be used where slim, parallel board mounting is required such as in single board computer host modules with the addition of expander cards or option cards, as illustrated in Figure 1-1. The PMC may be mounted with instruments and panels that comply with the requirements of IEEE Std 1386 [1].

For maximum utilization of component space, the mezzanine card is typically placed such that the major component side (side one) of the mezzanine card faces the major component side (side one) of the host board.

# 1.4 Dimensions

All mechanical dimensions are specified in P1386 [1]. All dimensions are in millimeters.

<sup>&</sup>lt;sup>1</sup> The numbers in brackets correspond to those of the references in Section 2.

Figure 1-1

Typical PMC Mounted to a Host Module

# 2. References

The following publications are used in conjunction with this standard:

- [1] IEEE P1386 Standard Mechanics for a Common Mezzanine Card Family: CMC <sup>2</sup>

- [2] PCI Local Bus Specification, Revision 2.2 1998 <sup>3</sup>

When any of the above specifications are superseded by an approved revision, that revision shall apply.

#### 2.1 Trademarks

The following names used within this draft standard are trademarked:

PICMG and CompactPCI are registered trademarks of the PCI Industrial Computers Manufacturers Group.

# 3. Definitions, Abbreviations and Terminology

# 3.1 Special Word Usage

**shall,** A key word indicating a mandatory requirement. Designers shall implement such mandatory requirements to ensure interchangeably and to claim conformance with the specification. The phrase is *required* is used interchangeably with the key word *shall*.

**should,** A key word indicating flexibility of choice with a strongly preferred implementation. The phrase is *recommended* and the word *preferred* are used interchangeably with the key word *should*.

**may,** A key word indicating flexibility of choice with no implied preference. The phrase is *optional* is used interchangeably with the key word *may*.

# 4. Mechanics and Compliance

# 4.1 Conformance

A vendor of host modules or mezzanine cards may claim compliance to the P1386.1 (PMC) standard if there are no areas of conflict between the host design and the P1386 [1] or P1386.1 standards. In addition, the vendor claiming compliance shall specify in the product specifications those areas of compliance where optional features are allowed.

<sup>2</sup> IEEE publications are available from the institute of Electrical and Electronics Engineers, Service Center, 445 Hoes Lane. PO Box 1331, Piscataway, NJ 08855-1331, USA. www.ieee.org

<sup>3</sup> PCI Specifications are available from PCI Special Interest Group 2575 NE Kathryn Street, #17, Hillsboro, Oregon 97124, USA, www.pcisig.com

# 4.2 PMC Voltage Keying

The PCI bus uses either 3.3V or 5V for signaling bus levels. A voltage keying is required to prevent association of host slots and mezzanine card with incompatible signaling voltages. The host shall indicate in its product specification which signaling voltage it uses and has been keyed for. Note that the mezzanine card may be designed to accept either or both signaling voltages.

For keying mechanics see P1386 [1].

# 4.3 Connector Configurations

The 32 bit PCI bus requires two 64 pin connectors, Pn1/Jn1 and Pn2/Jn2. The 64 bit PCI bus requires three 64 pin connectors, Pn1/Jn1, Pn2/Jn2 and Pn3/Jn3. When I/O is routed through the host's backplane, the Pn4/Jn4 connector is required for routing of the I/O signals. Any combination of the three connector functions may be used on the mezzanine card as well as on the host.

# 4.4 Power Consumption, Heat Dissipation and Air Flow

Each PMC vendor shall document in the product's information the current drawn on the 5V and 3.3V power pins. The average heat dissipated on both sides shall be given as well as the average percent of area, side view, occupied by the components. A user can then calculate the amount of air flow that can be expected to flow across each mezzanine card as well as the amount of air needed to properly cool the mezzanine card.

# 4.5 Electromagnetic Compatibility

Each PMC vendor shall document in the product's literature to which Electromagnetic Compatibility (EMC) standards and to what level(s) the product was designed and tested to (if tests were performed).

## 4.6 Shock and Vibration

Each PMC vendor shall document in the product's literature to which shock and vibration standards and to what level(s) the product was designed and tested to (if tests were performed).

#### 4.7 Environmental

Each PMC vendor shall document in the product's literature to which environmental standards and to what level(s) the product was designed and tested (if tests were performed).

#### **4.8 MTBF**

Each PMC vendor shall state in the product's literature the calculated MTBF (mean-time-between-failure) for which environmental level and state what method was used to calculate the MTBF number(s).

# 5. Electrical and Logical Layer

#### **5.1 Connector Utilization**

The PMC and associated host connector pin assignments are based on specific signal integrity rules as well as power distribution. The 5V pins are assigned to Pn1/Jn1 connector, the 3.3V pins are assigned to Pn2/Jn2 connector and the V(I/O) to Pn1/Jn1 and Pn3/Jn3 connectors. All signal pins are adjacent to a voltage or ground pin with the CLK (clock) pin surrounded by three ground pins.

The Pn1/Jn1 and Pn2/Jn2 connectors are always present and contain the signals for the 32 bit PCI Bus. When the PCI Bus is expanded to 64 bits, the Pn3/Jn3 connector is used for these signals. User defined I/O signals are assigned to the Pn4/Jn4 connector. The Pn3/Jn3 and Pn4/Jn4 connectors do not need to be present on either the PCI Mezzanine Card or the host when those signals are not used. Use of PCI Bus reserve (PCI-RSVD) and PMC (PMC-RSVD) reserved pins are not allowed as their use may be defined by future versions of the PCI specifications or by this standard, respectively. All Pn1/Jn1 and Pn2/Jn2 connector pins are fixed and shall not be reassigned to other functions.

Note that the PCI signals are completely defined in reference (2), PCI Local Bus Specification.

Pn4/Jn4 connectors are for user defined I/O functions. The mapping of these I/O signals to the backplane is defined in the P1386 (CMC) Standard [1] for VME and Multibus applications. Mapping of I/O signals off the rear of CompactPCI boards through CompactPCI backplanes is defined and controlled by PICMG, www.PICMG.com.

#### **5.2 PMC Connector Pin Assignment**

PCI Mezzanine Cards and associated hosts that support PMC slots shall assign the local bus signal pins per the pin assignment given in Table 5-1.

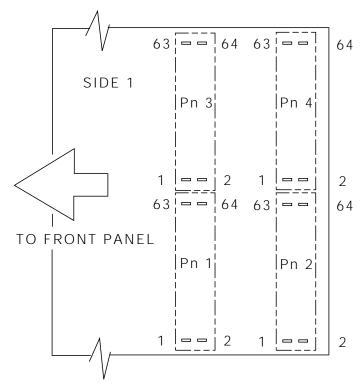

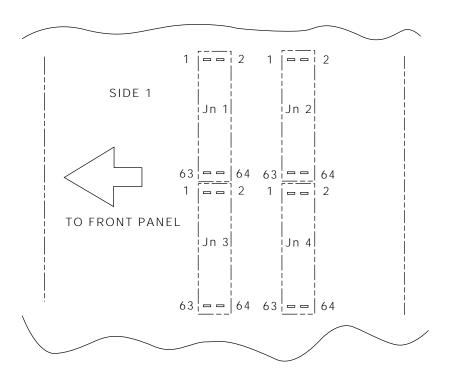

See Figures 5-1 and 5-2 for connector orientation on the PMC and on the associated host, respectively.

Table 5-1

PMC Connectors Pin Assignments

| Pn1/Jn1 32 Bit PCI |           |           |     |     | Pn2/Jn2 32 Bit PCI |           |     |  |

|--------------------|-----------|-----------|-----|-----|--------------------|-----------|-----|--|

| Pin                | Signal    | Signal    | Pin | Pin | Signal             | Signal    | Pin |  |

| 1                  | TCK       | -12V      | 2   | 1   | +12V               | TRST#     | 2   |  |

| 3                  | Ground    | INTA#     | 4   | 3   | TMS                | TDO       | 4   |  |

| 5                  | INTB#     | INTC#     | 6   | 5   | TDI                | Ground    | 6   |  |

| 7                  | BUSMODE1# | +5V       | 8   | 7   | Ground             | PCI-RSVD* | 8   |  |

| 9                  | INTD#     | PCI-RSVD* | 10  | 9   | PCI-RSVD*          | PCI-RSVD* | 10  |  |

| 11                 | Ground    | 3.3Vaux   | 12  | 11  | BUSMODE2#          | +3.3V     | 12  |  |

| 13                 | CLK       | Ground    | 14  | 13  | RST#               | BUSMODE3# | 14  |  |

| 15                 | Ground    | GNT#      | 16  | 15  | 3.3V               | BUSMODE4# | 16  |  |

| 17                 | REQ#      | +5V       | 18  | 17  | PME#               | Ground    | 18  |  |

| 19                 | V (I/O)   | AD[31]    | 20  | 19  | AD[30]             | AD[29]    | 20  |  |

| 21                 | AD[28]    | AD[27]    | 22  | 21  | Ground             | AD[26]    | 22  |  |

| 23                 | AD[25]    | Ground    | 24  | 23  | AD[24]             | +3.3V     | 24  |  |

| 25                 | Ground    | C/BE[3]#  | 26  | 25  | IDSEL              | AD[23]    | 26  |  |

| 27                 | AD[22]    | AD[21]    | 28  | 27  | +3.3V              | AD[20]    | 28  |  |

| 29                 | AD[19]    | +5V       | 30  | 29  | AD[18]             | Ground    | 30  |  |

| 31                 | V (I/O)   | AD[17]    | 32  | 31  | AD[16]             | C/BE[2]#  | 32  |  |

| 33                 | FRAME#    | Ground    | 34  | 33  | Ground             | PMC-RSVD  | 34  |  |

| 35                 | Ground    | IRDY#     | 36  | 35  | TRDY#              | +3.3V     | 36  |  |

| 37                 | DEVSEL#   | +5V       | 38  | 37  | Ground             | STOP#     | 38  |  |

| 39                 | Ground    | LOCK#     | 40  | 39  | PERR#              | Ground    | 40  |  |

| 41                 | PCI-RSVD* | PCI-RSVD* | 42  | 41  | +3.3V              | SERR#     | 42  |  |

| 43                 | PAR       | Ground    | 44  | 43  | C/BE[1]#           | Ground    | 44  |  |

| 45                 | V (I/O)   | AD[15]    | 46  | 45  | AD[14]             | AD[13]    | 46  |  |

| 47                 | AD[12]    | AD[11]    | 48  | 47  | M66EN              | AD[10]    | 48  |  |

| 49                 | AD[09]    | +5V       | 50  | 49  | AD[08]             | +3.3V     | 50  |  |

| 51                 | Ground    | C/BE[0]#  | 52  | 51  | AD[07]             | PMC-RSVD  | 52  |  |

| 53                 | AD[06]    | AD[05]    | 54  | 53  | +3.3V              | PMC-RSVD  | 54  |  |

| 55                 | AD[04]    | Ground    | 56  | 55  | PMC-RSVD           | Ground    | 56  |  |

| 57                 | V (I/O)   | AD[03]    | 58  | 57  | PMC-RSVD           | PMC-RSVD  | 58  |  |

| 59                 | AD[02]    | AD[01]    | 60  | 59  | Ground             | PMC-RSVD  | 60  |  |

| 61                 | AD[00]    | +5V       | 62  | 61  | ACK64#             | +3.3V     | 62  |  |

| 63                 | Ground    | REQ64#    | 64  | 63  | Ground             | PMC-RSVD  | 64  |  |

Note: For PCI-RESVD/PMC Pin Relationship see Table 5-3

Table 5-1 (Concluded)

PMC Connectors Pin Assignments

| PMC Connectors Pin Assignments |          |          |     |     |              |             |     |  |

|--------------------------------|----------|----------|-----|-----|--------------|-------------|-----|--|

| Pn3/Jn3 64 Bit PCI             |          |          |     |     | Pn4/Jn4 User | Defined I/O |     |  |

| Pin                            | Signal   | Signal   | Pin | Pin | Signal       | Signal      | Pin |  |

| 1                              | PCI-RSVD | Ground   | 2   | 1   | I/O          | I/O         | 2   |  |

| 3                              | Ground   | C/BE[7]# | 4   | 3   | I/O          | I/O         | 4   |  |

| 5                              | C/BE[6]# | C/BE[5]# | 6   | 5   | I/O          | I/O         | 6   |  |

| 7                              | C/BE[4]# | Ground   | 8   | 7   | I/O          | I/O         | 8   |  |

| 9                              | V (I/O)  | PAR64    | 10  | 9   | I/O          | I/O         | 10  |  |

| 11                             | AD[63]   | AD[62]   | 12  | 11  | I/O          | I/O         | 12  |  |

| 13                             | AD[61]   | Ground   | 14  | 13  | I/O          | I/O         | 14  |  |

| 15                             | Ground   | AD[60]   | 16  | 15  | I/O          | I/O         | 16  |  |

| 17                             | AD[59]   | AD[58]   | 18  | 17  | I/O          | I/O         | 18  |  |

| 19                             | AD[57]   | Ground   | 20  | 19  | I/O          | I/O         | 20  |  |

| 21                             | V (I/O)  | AD[56]   | 22  | 21  | I/O          | I/O         | 22  |  |

| 23                             | AD[55]   | AD[54]   | 24  | 23  | I/O          | I/O         | 24  |  |

| 25                             | AD[53]   | Ground   | 26  | 25  | I/O          | I/O         | 26  |  |

| 27                             | Ground   | AD[52]   | 28  | 27  | I/O          | I/O         | 28  |  |

| 29                             | AD[51]   | AD[50]   | 30  | 29  | I/O          | I/O         | 30  |  |

| 31                             | AD[49]   | Ground   | 32  | 31  | I/O          | I/O         | 32  |  |

| 33                             | Ground   | AD[48]   | 34  | 33  | I/O          | I/O         | 34  |  |

| 35                             | AD[47]   | AD[46]   | 36  | 35  | I/O          | I/O         | 36  |  |

| 37                             | AD[45]   | Ground   | 38  | 37  | I/O          | I/O         | 38  |  |

| 39                             | V (I/O)  | AD[44]   | 40  | 39  | I/O          | I/O         | 40  |  |

| 41                             | AD[43]   | AD[42]   | 42  | 41  | I/O          | I/O         | 42  |  |

| 43                             | AD[41]   | Ground   | 44  | 43  | I/O          | I/O         | 44  |  |

| 45                             | Ground   | AD[40]   | 46  | 45  | I/O          | I/O         | 46  |  |

| 47                             | AD[39]   | AD[38]   | 48  | 47  | I/O          | I/O         | 48  |  |

| 49                             | AD[37]   | Ground   | 50  | 49  | I/O          | I/O         | 50  |  |

| 51                             | Ground   | AD[36]   | 52  | 51  | I/O          | I/O         | 52  |  |

| 53                             | AD[35]   | AD[34]   | 54  | 53  | I/O          | I/O         | 54  |  |

| 55                             | AD[33]   | Ground   | 56  | 55  | I/O          | I/O         | 56  |  |

| 57                             | V (I/O)  | AD[32]   | 58  | 58  | I/O          | I/O         | 58  |  |

| 59                             | PCI-RSVD | PCI-RSVD | 60  | 59  | I/O          | I/O         | 60  |  |

| 61                             | PCI-RSVD | Ground   | 62  | 61  | I/O          | I/O         | 62  |  |

| 63                             | Ground   | PCI-RSVD | 64  | 63  | I/O          | I/O         | 64  |  |

Figure 5-1 Connector Orientation on PMC, Side 1

Figure 5-2 Connector Orientation on Host, Side 1

# 5.3 Comparison of Pin Usage, PCI to PMC

For reference purposes, a comparison of pin usage, PCI to PMC is provided in Table 5-2 below, where all the four 64-pin connectors are implemented.

Table 5-2

Pin Use Comparison PCI to PMC (Single Size)

| Till Osc Comparison Tel to Tille (Single Size) |                 |     |     |  |  |

|------------------------------------------------|-----------------|-----|-----|--|--|

| Power Pins                                     | <b>Bus Pins</b> | PCI | PMC |  |  |

| + 5V                                           |                 | 8   | 6   |  |  |

| + 12V                                          |                 | 1   | 1   |  |  |

| - 12V                                          |                 | 1   | 1   |  |  |

| + 3.3V                                         |                 | 12  | 9   |  |  |

| V (I/O                                         |                 | 11  | 8   |  |  |

| Ground                                         |                 | 42  | 43  |  |  |

| Subtotal                                       |                 | 75  | 69  |  |  |

|                                                | Signals         | 100 | 101 |  |  |

|                                                | BUSMODE         | 2   | 4   |  |  |

|                                                | I/O             | 0   | 64  |  |  |

|                                                | PCI             | 11  | 11  |  |  |

|                                                | PMC             | 0   | 8   |  |  |

|                                                | Subtotal        | 113 | 187 |  |  |

|                                                | Total Pins      | 188 | 256 |  |  |

# 5.4 Mapping of PCI Reserve Pins

In the future, should one or more of the PCI reserved pins become assigned to a new function, the assignment to the PMC connector shall be consistent. Table 5-3 lists the assignment of these reserved pins to the PMC connector. It will not be necessary to update this draft standard whenever this occurs.

Assignment of PMC reserved pins will require an update to this standard.

Table 5-3

PCI-Reserved/PMC Relationship

|          |            |          | /          |

|----------|------------|----------|------------|

| PCI-RSVD | PMC Signal | PCI-RSVD | PMC Signal |

| 9A       | Pn2-8      | 63B      | Pn3-1      |

| 10B      | Pn2-9      | 92A      | Pn3-59     |

| 11A      | Pn2-10     | 92B      | Pn3-60     |

| 14B      | Pn1-10     | 93B      | Pn3-61     |

| 40A      | Pn1-41     | 94A      | Pn3-64     |

| 41A      | Pn1-42     |          |            |