Approved as an American National Standard by

# American National Standard for The Mezzanine Concept M-Module Specification

# Secretariat VMEbus International Trade Association

Approved May 20, 1997 American National Standards Institute, Inc.

American National Standard for M-Module

# Secretariat VMEbus International Trade Association

Approved May 20, 1997 American National Standards Institute, Inc.

# Abstract

This specification defines minimum mechanical and electrical characteristics of M-Modules, a method of implementing modular circuit boards with specific functions that can be used to add functionality to other larger printed circuit boards.

# American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether they have approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standard Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

Published by

# VMEbus International Trade Association 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260

Copyright © 1997 by VMEbus International Trade Association All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of the publisher.

Printed in the United States of America - R1.0 ISBN 1-885731-07-8

# Contents

|       | Page                                                               |

|-------|--------------------------------------------------------------------|

| Forev | vord                                                               |

| 1     | Scope and purpose 1                                                |

| 2     | Normative references                                               |

| 3     | Conventions 1                                                      |

| 4     | M-Module characteristics                                           |

| 5     | Basic electrical specification                                     |

| 6     | Mechanical specification                                           |

| 7     | Thermal specification                                              |

| 8     | Extended electrical specification                                  |

| Table | es                                                                 |

| 1     | Characteristics of M-Modules and their designation                 |

| 2     | Signal name and type                                               |

| 3     | Electrical specification of the drivers over the whole temperature |

|       | range                                                              |

| 4     | Timing parameters                                                  |

| 5     | Pin assignment                                                     |

| 6     | Recommendation for correspondence between 25-pin D-Sub             |

|       | connector and 24-pin peripheral connector                          |

| 7     | Data bus routing                                                   |

| 8     | Signal name and type                                               |

| 9     | Timing parameters                                                  |

| 10    | Pin assignment                                                     |

| Figur | es                                                                 |

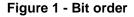

| 1     | Bit order                                                          |

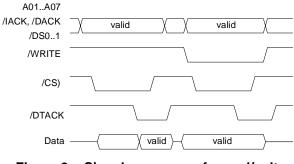

| 2     | Signal sequence of a read/write access                             |

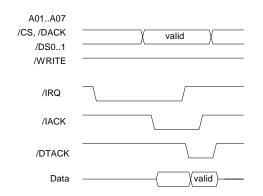

| 3     | Signal sequence of an interrupt with hardware-end-of-interrupt 5   |

| 4     | Signal sequence of interrupt vector transfer cycle                 |

| 5     | Timing                                                             |

| 6     | Command transfer to the EEPROM                                     |

| 7     | Sample circuit for a module with module identification             |

| 8     | Power-up and power-down                                            |

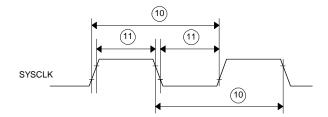

| 9     | SYSCLK timing                                                      |

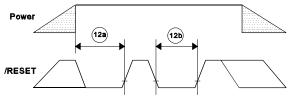

| 10    | /RESET timing                                                      |

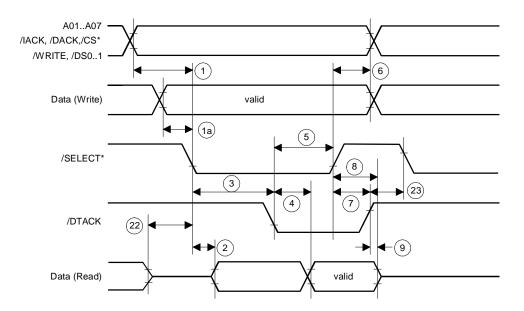

| 11    | Read/write timing                                                  |

| 12   | Interrupt request timing                                      | 10 |

|------|---------------------------------------------------------------|----|

| 13   | DMA request timing                                            | 10 |

| 14   | Orientation of the receptacle connector on the module         | 12 |

| 15   | Orientation of the 24-pin receptacle connector on the module  | 13 |

| 16   | Orientation of the 10-pin receptacle connectors on the module | 15 |

| 17   | Intermodule connector, cross section (point-to-point wiring)  | 15 |

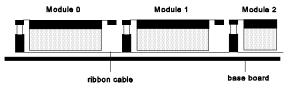

| 18   | Intermodule connection, cross section (bus connection)        | 15 |

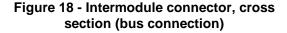

| 19   | Dimensions of a single MA-Module and position of connectors   | 16 |

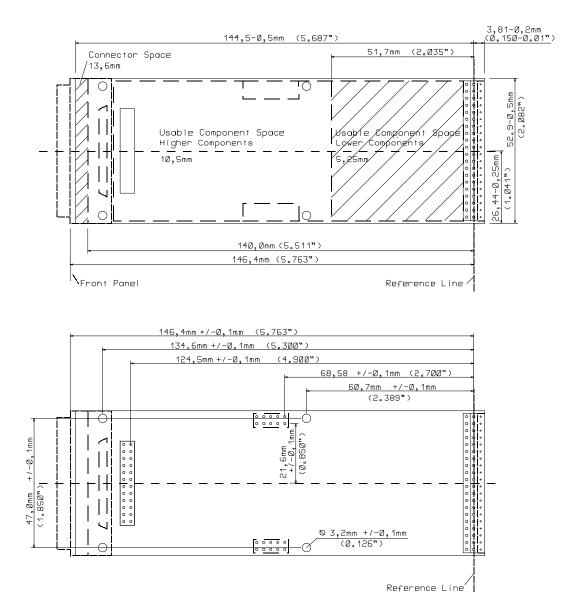

| 20   | Example for mounting a single MA-Module on a base board       | 16 |

| 21   | Dimensions of a double MA-Module                              | 17 |

| 22   | Position of connectors                                        | 18 |

| 23   | Dimensions of a triple MA-Module                              | 19 |

| 24   | Position of connectors                                        | 20 |

| 25   | M-Module front                                                | 21 |

| 26   | M-Module connectors                                           | 21 |

| 27   | Bit order                                                     | 23 |

| 28   | Data bus routing                                              | 24 |

| 29   | Signal sequence of a read/write access                        | 25 |

| 30   | Burst transfer sequence for write transfers                   | 26 |

| 31   | TRIGA and TRIGB timing                                        | 26 |

| 32   | Read/write timing                                             | 27 |

| 33   | Orientation of the receptacle connector on the module         | 28 |

| Anne | exes                                                          |    |

| Α    | Software driver interface                                     | 29 |

| В    | Conformance test specification                                | 47 |

#### Foreword

There is a relatively large choice of I/O boards for standard bus systems such as the VMEbus.

Boards with the Single Eurocard and Double Eurocard formats are particularly widespread. The Double Eurocard format has the advantage of better utilization of volume and lower overhead for the bus interface. Single Eurocards have the advantage of greater modularity but do not permit peripheral equipment to be connected on the bus side with a second connector. Both concepts are relatively rigid when it comes to implementing custom solutions.

The search for a solution that would combine the advantages of both formats at low cost and allow a large degree of flexibility for different applications led to the development of the M-Modules.

| Criterion                            | Single Eurocard | Double Eurocard | M-Module  |

|--------------------------------------|-----------------|-----------------|-----------|

| Volume utilization                   | poor            | good            | very good |

| Connection capabilites               | very poor       | very good       | very good |

| Overhead for bus interface           | very high       | low             | low       |

| Expense for small applications       | low             | very high       | very low  |

| Expense for medium-size applications | high            | high            | low       |

| Expense for large applications       | very high       | low             | low       |

| Service costs                        | low             | high            | low       |

| Flexibility                          | high            | low             | very high |

| Effort for custom development        | low             | high            | very low  |

| Comparison of I/O concepts: | Com | oarison | of I/O | concepts: |

|-----------------------------|-----|---------|--------|-----------|

|-----------------------------|-----|---------|--------|-----------|

#### Advantages of M-Modules and MA-Modules

- up to four (different) modules per Double Eurocard base board

- two methods of connecting peripherals:

- direct, using the front panel

- indirect, via the base board using a 24-pin connector

- uncomplicated interface to the base board

- 16-bit or 32-bit data bus

- 8-bit and 24-bit address bus

- interrupt and DMA capabilities

- module identification facility

- trigger lines

- optimum utilization of area and volume

- good thermal characteristics

- high mechanical stability

- open bus specification

- wide range of modules available through cooperation between vendors

There are two annexes in this standard. Annexes A and B are informative and are not considered part of this standard.

This M-Module specification was prepared by the Manufacturers and Users of M-Modules association.

Suggestions for improvement of this standard will be welcome. They should be sent to MUMM association, Simon-Schöffel-Straße 21, 90427 Nürnberg, Germany.

This standard was processed and approved for submittal to ANSI by Accredited Standards Committee on [title and alphanumerical designation of committee]. Committee approval of the standard does not necessarily imply that all committee members voted for its approval. At the time it approved this standard, the [designation] Committee had the following members:

Name, Chairman Name, Vice-Chairman Name, Administrative Secretary

Organization RepresentedName of Representativexxxxxxnamexxxxxxnamexxxxxxnamexxxxxxnamexxxxxxnamexxxxxxname

# VITA Standard

for Modular Industrial Computers-

# The Mezzanine Concept-M-Module Specification

1 Scope and purpose

# 1.1 Scope

This specification defines minimum mechanical and electrical characteristics of M-Modules, with the aim of ensuring that any M-Module can be used on any base board capable of being fitted with M-Modules. Also conceivable are base boards for special applications that can be fitted both with M-Modules according to this standard and with specialized modules that can only be used with the particular base board. This means that the user has access to a wide variety of standardized M-Modules but is not prevented from developing or using specialized (non-standard) modules.

For instance, the basic electrical specification specifies modules with a 2-row connector for communication between the base board and the module. All modules which comply with the minimum requirements of this specification are designated M-Modules.

For special requirements, a third row can be added to the base board connection. This is described in the mechanical specification. The use of the additional signals or extended use of existing signals (in compliance with the basic electrical specification) can be standardized to a certain extent. Therefore, certain signals and signal groups are defined in the extended electrical specification as regards their function, timing and electrical characteristics. Modules complying with these additional specifications are designated MA-Modules.

# 1.2 Purpose

The M-Module concept is deliberately designed to allow specialized modules to be developed simply, quickly and cheaply. These specialized development efforts can be undertaken by different vendors or by the customers themselves.

# 2 Normative references

The following standards contain provisions which, through reference in this text, constitute provisions of this VITA standard. At the time of publication, the editions indicated were valid. All standards are subject to revision, and parties to agreements based on this VITA standard are encouraged to investigate the possibility of applying the most recent editions of the standards indicated below.

IEC 68-2-6, *Basic Environmental Testing Procedures*. *Part 2: Tests. Test Fc and guidance: Vibration*; International Electrotechnical Commission; 1982

IEC 68-2-27, Environmental testing. Part 2: Tests. Test Ea and guidance: Shock; IEC; 1987

IEC 68-2-29, Basic environmental testing procedures. Part 2: Tests. Test Eb and guidance: Bump; IEC; 1987

DIN 40040, Applicability classes and reliability figures for components of telecommunications and electronics; Deutsches Institut für Normung, Burggrafenstr. 6, 10787 Berlin; April 1987

DIN 85-M3x8, *Flachkopfschraube mit Schlitz*; Deutsches Institut für Normung, Burggrafenstr. 6, 10787 Berlin

# 3 Conventions

#### 3.1 Use of the slash

A slash preceding the name of signals that are levelsignificant denotes that the signal is valid when it has "L" potential.

A slash preceding the name of signals that are edgesignificant denotes that the actions triggered by that signal occur on a high to low transition.

#### 3.2 Hexadecimal numbers

Hexadecimal numbers are preceded by "0x".

# 4 M-Module characteristics

Characteristics of modules as regards their interface with the base board are given a fixed designation. Specific characteristics must then correspond to capabilities of the base board for this function to be used. For instance, a module which can generate an interrupt is designated an "interrupter". If it is desired to make use of this capability on the base board, then the latter must be capable of handling interrupts - it must be an "interrupt handler". An interrupter M-Module can be used on a base board that cannot handle interrupts, but in that case without interrupts.

For instance, an MA-Module can be used only with functional limitations on a base board suitable only for M-Modules. If the MA-Module has 24-bit addresses (A24) and requires these, it cannot be used on base boards that have only 8 bit addresses.

| Table 1 - | Characteristics | of M-Modules and | d their designation |

|-----------|-----------------|------------------|---------------------|

|           |                 |                  |                     |

| Module                                                                                | Characteristics                                                                                                                                               |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M-Module                                                                              | Module which complies with the M-Module Specification and has a 2-row, 40-pin connector for communication with the base board                                 |

| MA-Module                                                                             | Module which complies with the M-Module specification and the MA-Module specification and has a 3-row, 60-pin connector for communication with the base board |

| A08                                                                                   | M-Module with an I/O address space of max. 256 bytes                                                                                                          |

| A24                                                                                   | MA-Module with a memory address space of max. 16 Mbytes                                                                                                       |

| D08                                                                                   | M-Module with an 8-bit data bus (D00D07)                                                                                                                      |

| D16                                                                                   | M-Module with a 16-bit data bus (D00D15)                                                                                                                      |

| D32                                                                                   | MA-Module with a 32-bit data bus (D00D31)                                                                                                                     |

| INTA M-Module with interrupt-request capabilities (type A, software-end-of-interrupt) |                                                                                                                                                               |

| INTB                                                                                  | M-Module with interrupt-request capabilities (type B, hardware-end-of-interrupt without vector transfer)                                                      |

| INTC                                                                                  | M-Module with interrupt-request capabilities (type C, hardware-end-of-interrupt with vector transfer)                                                         |

| DMA08                                                                                 | M-Module with an 8-bit DMA interface (using D00D07)                                                                                                           |

| DMA16                                                                                 | M-Module with a 16-bit DMA interface (using D00D15)                                                                                                           |

| DMA32                                                                                 | MA-Module with a 32-bit DMA interface (using D00D31)                                                                                                          |

| TRIGI                                                                                 | MA-Module with trigger inputs                                                                                                                                 |

| TRIGO                                                                                 | MA-Module with trigger outputs                                                                                                                                |

| IDENT                                                                                 | M-Module with identification                                                                                                                                  |

| M-Module characteristics are hardware-stored in a serial EEPROM. Information is coded in 16 16-bit words as described in the following overview. The basic electrical specification contains a detailed description of the EEPROM |                           |                                                                             | - D09                                                         | '0'<br>'1'                                                                                                     | module without trigger inputs<br>module with trigger inputs<br>(TRIGI)             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| specification<br>EEPROM.<br><u>Word 0 (sync.</u>                                                                                                                                                                                  | -                         | - D08D07                                                                    | '00'<br>'01'<br>'10'<br>'11'                                  | no DMA requester<br>8-bit DMA (DMA08)<br>16-bit DMA (DMA16)<br>32-bit DMA (DMA32)                              |                                                                                    |

| - D15D00<br><u>Word 1 (modu</u><br>- D15D00<br>Word 2 (ravis                                                                                                                                                                      | lle number (binary coded) | - D06D05                                                                    | '00'<br>'01'<br>'10'<br>'11'                                  | no interrupter<br>interrupter method a) (INTA)<br>interrupter method b) (INTB)<br>interrupter method c) (INTC) |                                                                                    |

| Word 2 (revision number):         - D15D00       revision number (binary coded)         Word 3 (module characteristics):                                                                                                          |                           |                                                                             | - D04D03                                                      | '00'<br>'01'<br>'10'<br>'11'                                                                                   | 8-bit data bus (D08)<br>16-bit data bus (D16)<br>32-bit data bus (D32)<br>reserved |

| - D15<br>- D14<br>- D13                                                                                                                                                                                                           | '0'<br>'1'<br>reserv      |                                                                             | - D02D01                                                      | '00'<br>'01'<br>'10'<br>'11'                                                                                   | 8-bit address bus (A08)<br>reserved<br>reserved<br>24-bit address bus (A24)        |

| - D12                                                                                                                                                                                                                             | '0'<br>'1'                | module does not need $\pm 12V$<br>module does need $\pm 12V$                | - D00                                                         | '0'                                                                                                            | M-Module does not support<br>m e m o r y                                           |

| - D11                                                                                                                                                                                                                             | '0'<br>'1'                | module does not need $+$ 5V module does need $+$ 5V                         |                                                               | '1'                                                                                                            | access<br>M-Module supports<br>m e m o r y                                         |

| - D10                                                                                                                                                                                                                             | '0'<br>'1'                | module without trigger<br>outputs<br>module with trigger outputs<br>(TRIGO) | <u>Words 47:</u><br>- D15D00<br><u>Words 815:</u><br>- D15D00 |                                                                                                                | access<br>00 reserved<br>defined                                                   |

|                                                                                                                                                                                                                                   |                           |                                                                             | D15D00                                                        | user-                                                                                                          | utilitu                                                                            |

- 5 Basic electrical specification

- 5.1 Communication between M-Module and base board

# Every M-Module

- can be accessed via a 16-bit data bus;

- has an I/O address space of 256 bytes, or 128 words;

- may be capable of generating interrupts and requesting a DMA transfer.

- 5.1.1 Signals

- D00..D15 Bidirectional data bus. D00 is the least significant data bit, D15 is the most significant.

| MSB | D15D08 | D07D00 | LSB |

|-----|--------|--------|-----|

|-----|--------|--------|-----|

If the M-Module has only an 8-bit data bus, only D00..D07 shall be used, i.e. every second byte is used in a 16-bit structure.

- A01..A07 Unidirectional address bus (input signals). A01 is the least significant address bit, A07 is the most significant. The 7 address bits make it possible to distinguish between 128 words on each module. A00 is not present. Differentiation between the two bytes of the word is made by lines DS0 and DS1 (q.v.).

- /WRITE Input signal. If this signal is "L", the data bus (when active) is directed toward the module. If this signal is "H", the data bus is directed away from the module (if allowed).

/CS Input signal. If this signal is active, the module is being accessed. While /CS is "L", the address bus, /WRITE, DSO, and DS1 are valid; on write access (/WRITE is "L") the data bus is also valid. For read access, the module must keep the data stable as long as /CS is active.

/DTACK Output signal. With this signal, the module terminates access when /CS is "L". A defined period of time later, the /CS signal is deasserted. For read access, the data must remain available for a defined period of time after /DTACK (until /CS is deasserted).

/DS0..1 Input signals. They are valid while /CS, /IACK or /DACK is active. When DS0 is "L", the data bus is active from D00 to D07; when DS1 is "L", the data bus is active from D08 to D15. When DS0 and DS1 are "L", a 16-bit access to the complete word is performed. When /CS is active, at least one of DS0 and DS1 is active.

| / <u>DS</u> O | / <u>DS1</u> | D <u>00D0</u> 7 | D <u>08D</u> 15 |

|---------------|--------------|-----------------|-----------------|

| "L"           | "L"          | transfer        | transfer        |

|               |              |                 |                 |

| "H"           | "L"          | no transfer     | transfer        |

| "L"           | "H"          | transfer        | no transfer     |

| "H"           | "H"          | invalid         |                 |

- /RESET Input signal. Resets the module to a defined state. It is normally activated on power-up.

- /IRQ Output signal. The module can generate an interrupt by setting "L" at this pin. This signal must remain until the interrupt is reset by /IACK or software.

- /IACK Input signal. /IACK acknowledges a pending interrupt. It is a matter for the module concerned to decide whether this signal is used to reset the interrupt or not. It is also for the module to decide whether it interprets this /IACK only as an "L" pulse of defined duration or as an access signal at which an interrupt vector has to be transmitted (via D00..D07). At all events, the signal is a reaction to the pending interrupt initiated by this module.

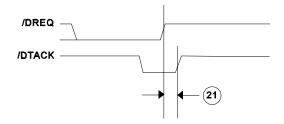

- /DREQ Output signal. A module can request a DMA transfer by setting "L" at this pin.

- /DACK Input signal. When it is "L", the base board performs a DMA transfer with this module. A read or write access is performed, but the /CS line is "H" and the address bus is invalid. With this cycle, the /DREQ line must be "H" if it is desired to prevent initiation of another DMA cycle.

- SYSCLK Input signal. 16-MHz clock, asynchronous to all other signals.

| GND   | Logical reference signal, power supply connection for the supply voltages. |

|-------|----------------------------------------------------------------------------|

| +5V   | Power supply connection.                                                   |

| +12V  | Power supply connection.                                                   |

| -12V  | Power supply connection.                                                   |

| 5.1.2 | Principles of operation                                                    |

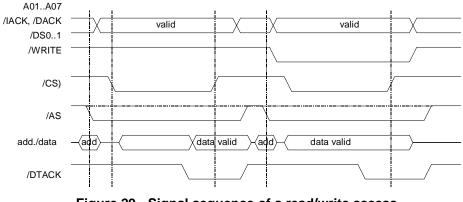

5.1.2.1 Read/write access

Neglecting interrupts, which are described elsewhere, data transfer can be divided into two different types of access - read access and write access. This distinction is expressed by the /WRITE signal. Timing is always the same, regardless of the number of bytes transferred in a cycle. How many bytes, and which bytes are transferred at one access, depends only on the signals /DS0 and /DS1. Timing during access is determined solely by the signals /CS and /DTACK. This substantially decreases the circuit complexity on the M-Modules.

Figure 2 - Signal sequence of a read/write access

If there are only ("fast") hardware registers on an M-Module, /DTACK and /CS can be linked with each other, which results in well-defined access times. 5.1.2.2 Interrupt

The module can generate an interrupt by activating the /IRQ line. It is not necessary for masking of the

interrupt to be possible. This can always be done on the base board. Depending on the module concerned, there are three methods of responding to an interrupt on the module:

# a) Type A, software-end-of-interrupt:

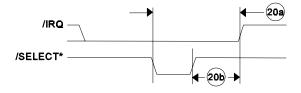

In the interrupt routine, the bus master resets the /IRQ line by accessing the module (for instance by reading a status register). At timing parameter #20a after the rising edge respectively #20b after the falling edge of /CS at the latest, the module shall de-activate the interrupt request line to signal that no further interrupt is pending.

#### b) Type B, hardware-end-of-interrupt:

At the beginning of the interrupt routine, an "L" pulse is set at the /IACK line of the module and this can be used to reset the /IRQ line. It is forbidden to assert /DTACK for this cycle. The width of the pulse is min. timing parameter #5 and max. timing parameter #3. At timing parameter #20a after the rising edge respectively #20b after the falling edge of /IACK at the latest, the module shall de-activate the interrupt request line to signal that no further interrupt is pending.

| /IRQ  | <b></b> |  |

|-------|---------|--|

| /IACK |         |  |

|       |         |  |

# Figure 3 - Signal sequence of an interrupt with hardware-end-of-interrupt

# c) Type C, interrupt vector transfer with hardware-endof-interrupt:

The base board generates an interrupt acknowledge cycle, differing from a normal read cycle in that /IACK is asserted instead of /CS. The module must make its vector available at D00..D07. The vector is transferred as byte information using D00..D07. The addresses remain unused.

At timing parameter #20a after the rising edge respectively #20b after the falling edge of /IACK or /CS at the latest, the module shall de-activate the interrupt request line to signal that no further interrupt is pending.

Figure 4 - Signal sequence of interrupt vector transfer cycle

#### Recommendation

Since it can be relatively difficult to construct base boards which support interrupt methods b) and c), all modules should have the alternative possibility of a "software-end-of-interrupt" (method a)).

#### 5.1.2.3 DMA transfer

Any module can use the /DREQ line to request the base board to perform a DMA cycle with the module. This normally requires a DMA controller on the base board. The DMA cycle is similar to a normal read or write access except that the /DACK line is asserted instead of /CS. The address bus is not used for this cycle. DMA transfer can be on a byte or word basis.

With the end of a cycle (before /DTACK is "H") the module must reset /DREQ to "H" if it is desired to prevent initiation of another DMA cycle.

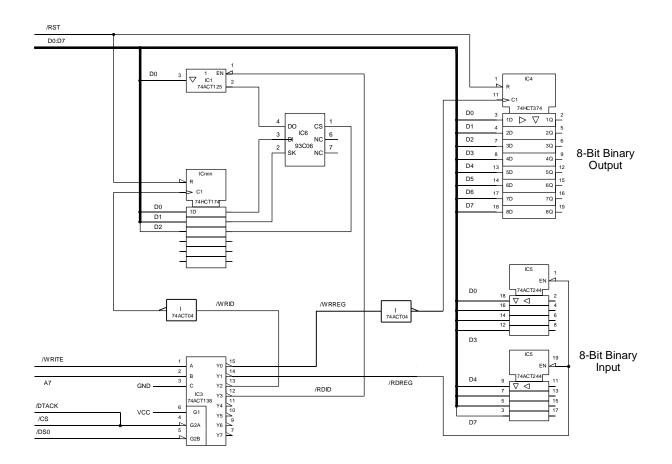

#### 5.1.2.4 Module identification

The identification of an M-Module is optional. It is accomplished using the read and write operations already described. No special lines are necessary. No special timing applies for the accesses. Identification is performed by accessing a serial EEPROM with an organization of 16 by 16 words. This EEPROM must be compatible with the standard IC (9306). Accesses are performed after reset by read or write operations to the highest module I/O address. If this address is required for other purposes during normal module operation, it is permissible to disable the EEPROM by accessing the addresses 0..0xfd. In this case accesses to the EEPROM are only possible after a reset.

Since serial EEPROMs have very long access times (several µs), the control and data signals required for access to the EEPROM are stored in registers on the M-Module. The shift timing is controlled by software. For this reason, the EEPROM's input signals are obtained from data lines D00..D02 using registers. The data input

is obtained from D00, the serial clock from D01 and the chip-select for the EEPROM from D02.

The registers are loaded by write operations in I/O space as appropriate with all address lines being "high". The serial information is read by read access to the same address. D00 represents the data output of the EEPROM.

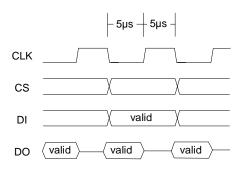

The software performing the access must ensure that the following timing is adhered to:

Notes

- 1 CLK = Clock (registered D01)

- 2 CS = Chip-Select (registered D02)

- 3 DI = Data input (registered D00)

- 4 DO = Data output (reading D00)

Figure 5 - Timing

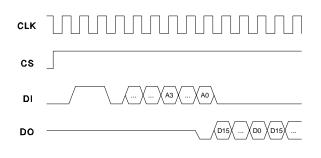

In order to read serial information, it is first necessary to transfer a command to the EEPROM. For this purpose the following sequence must be used:

Notes

- 1 CLK = Clock (registered D01)

- 2 CS = Chip-Select (registered D02)

- 3 DI = Data input (registered D00)

- 4 DO = Data output (reading D00)

Figure 6 - Command transfer to the EEPROM

Figure 7 - Sample circuit for a module with module identification

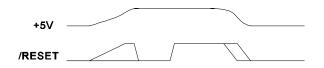

5.1.2.5 Power-up

After power-up, i.e. after all voltages are within the prescribed tolerances and the SYSCLK signal complies with the specification, the base board must ensure that the /RESET signal remains active at least for timing parameter #12a. After /RESET is asserted, all other lines must be inactive. To reset the module after powerup, /RESET must be activated at least for timing parameter #12b.

Figure 8 - Power-up and power-down

| C C              |                |        |

|------------------|----------------|--------|

| Signal name Type |                | 2      |

| D00D15           | TS I/O         | А      |

| A01A07           | input          | В      |

| /DS01            | input          | В      |

| /CS              | input          | В      |

| /WRITE           | input          | В      |

| /DTACK           | output         | С      |

| /IRQ             | output         | С      |

| /IACK            | input          | В      |

| /DREQ            | output         | С      |

| /DACK            | input          | В      |

| /RESET<br>SYSCLK | input<br>input | B<br>B |

| SISCLI           | mput           | D      |

5.1.3

**Driver Characteristics** Table 2 - Signal name and type

| Туре |                            | Parameter, characteristic                                  | Value   |

|------|----------------------------|------------------------------------------------------------|---------|

| A,B  | V <sub>ih</sub>            | Min. high-level input voltage                              | 2.2V    |

| A,B  | $\mathbf{V}_{\mathrm{il}}$ | Max. low-level input voltage                               | 0.8V    |

| A,B  | $I_{ih}$                   | Max. high-level input current                              | -0.05mA |

| A,B  | $I_{il}$                   | Max. low-level input current                               | 0.2mA   |

| A,C  | $V_{oh}$                   | Min. high-level output voltage (I <sub>out</sub> < 1.6 mA) | 2.4V    |

| A,C  | $V_{ol}$                   | Max. low-level output voltage ( $I_{out} < 1.6mA$ )        | 0.4V    |

| A,C  | $I_{oh}$                   | Min. high-level output current ( $V_{out} > 2.4V$ )        | 1.6mA   |

| A,C  | $I_{ol}$                   | Min. low-level output current ( $V_{out} < 0.4V$ )         | -1.6mA  |

Table 3 - Electrical specification of the drivers over the whole temperature range

The capacitive load of a pin must not exceed 25pF.

Normal controller chips fulfill these requirements, so, on modules including such controllers, it is not necessary to install data bus drivers. If it should be necessary to install data bus drivers for particularly simple modules without their own controller chips, types such as the 74ABT245 are suitable.

NOTE - It may be difficult to design a base board with both low-cost and high-performance design. Driver loads and bus driver should be carefully selected.

#### 5.1.4 Power supply

The power for the module is supplied via GND, +5V, +12V and -12V. The following specifications apply:

| Voltage | Tolerance | Max. current |

|---------|-----------|--------------|

|         |           |              |

| +5V     | +5%, -5%  | 1000mA       |

| -12V    | +5%, -5%  | 200mA        |

| +12V    | +5%, -5%  | 200mA        |

NOTE - The maximum currents indicated apply to M-Modules. Base boards must be designed in such a way that they can provide these power supplies.

Tolerance includes all ripple. However, one should bear in mind that the power supply must pass through various connectors and printed wiring. Every base board must be capable of supplying the module with all supply voltages using these lines.

5.1.5 Timing specifications

Figure 9 - SYSCLK timing

Figure 10 - /RESET timing

#### NOTES

\*: Only one of the three signals /CS, /DACK and /IACK is asserted (named "/SELECT") "L" during a cycle; the others are "H" as indicated in the following table. Timing parameter #1 is irrelevant for the /SELECT signal.

| Cycle type            | /CS | /DACK | /IACK |

|-----------------------|-----|-------|-------|

|                       |     |       |       |

| Normal access         | L   | Н     | Н     |

| DMA access            | Н   | L     | Н     |

| Interrupt acknowledge | Н   | Н     | L     |

#### NOTES

\*: Only one of the two signals /CS or /IACK is asserted (named "/SELECT") "L" during a cycle; the other is "H" as indicated in the following table. Timing parameter #1 is irrelevant for the /SELECT signal.

# Figure 13 - DMA request timing

| Hardware-end-of-interrupt | Н       | L           |

|---------------------------|---------|-------------|

| Vector transfer           | Н       | L           |

| Figure 12 - Interru       | pt requ | lest timing |

| Table 4 - Tim | ing parameters |

|---------------|----------------|

|---------------|----------------|

| No. | Characteristic                                                    | Min. | Max.  | Unit |

|-----|-------------------------------------------------------------------|------|-------|------|

| 1   | /WRITE, /DS01, /CS, /DACK, /IACK to /SELECT (Setup),<br>A01A07    | 10   | -     | ns   |

| 1a  | /D0015 to /SELECT (Setup)                                         | 0    | -     | ns   |

| 2   | /SELECT to data-out active                                        | 0    | -     | ns   |

| 3   | /SELECT to /DTACK                                                 | 0    | 10000 | ns   |

| 4   | /DTACK to data valid                                              | -    | 25    | ns   |

| 5   | /DTACK to /SELECT (Hold)                                          | 30   | -     | ns   |

| 6   | /SELECT to /WRITE, /DS01, /CS, /DACK, /IACK, A01A07, D0015 (Hold) | 10   | -     | ns   |

| 7   | /SELECT = "H" to /DTACK (Hold)                                    | 0    | 100   | ns   |

| 8   | /SELECT = "H" to data invalid (Hold)                              | 0    | -     | ns   |

| 9   | /DTACK = "H" to data-out high impedance                           | -    | 25    | ns   |

| 10  | SYSCLK cycle time                                                 | 61   | 64    | ns   |

| 11  | SYSCLK pulse width                                                | 22   | 40    | ns   |

| 12a | /RESET low time, at power up                                      | 200  | -     | ms   |

| 12b | /RESET low time, at normal operation                              | 1    | -     | μs   |

| 20a | /SELECT "L" to /IRQ inactive                                      | 0    | -     | μs   |

| 20b | /SELECT "H" to /IRQ inactive                                      | -    | 1     | μs   |

| 21  | /DREQ to end of cycle (/DTACK = "H")                              | 0    | -     | ns   |

| 22  | Data bus floating to /SELECT active                               | 0    | -     | ns   |

| 23  | /DTACK inactive to /SELECT active                                 | 25   | -     | ns   |

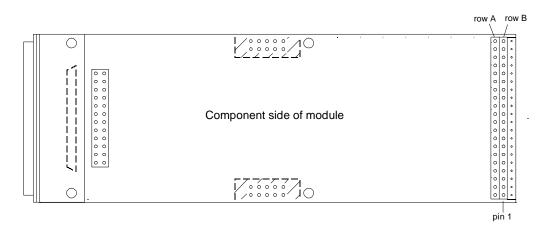

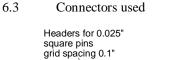

#### 5.1.6 Pin assignment

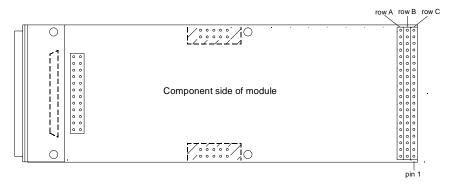

The control interface between the base board and the module is via two 20-pin plug connectors (pin headers) on the base board, which correspond to receptacles on the module.

| Pin | Row A  | Row B  |

|-----|--------|--------|

|     |        |        |

| 1   | /CS    | GND    |

| 2   | A01    | +5V    |

| 3   | A02    | +12V   |

| 4   | A03    | -12V   |

| 5   | A04    | GND    |

| 6   | A05    | /DREQ  |

| 7   | A06    | /DACK  |

| 8   | A07    | GND    |

| 9   | D08    | D00    |

| 10  | D09    | D01    |

| 11  | D10    | D02    |

| 12  | D11    | D03    |

| 13  | D12    | D04    |

| 14  | D13    | D05    |

| 15  | D14    | D06    |

| 16  | D15    | D07    |

| 17  | /DS1   | /DS0   |

| 18  | /DTACK | /WRITE |

| 19  | /IACK  | /IRQ   |

| 20  | /RESET | SYSCLK |

Table 5 - Pin assignment

# 5.2 Connecting peripherals

Peripheral equipment may be connected using a front

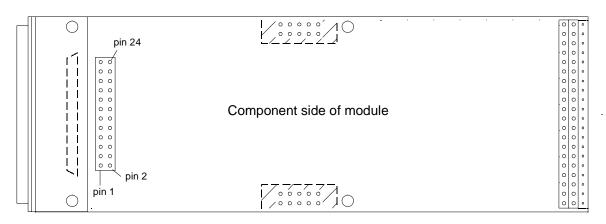

Figure 14 - Orientation of the receptacle connector on the module

panel connector, for instance a 25-pin D-Sub connector or by means of a 24-pin receptacle connector via the base board.

If the 24-pin receptacle connector is not used, the free space can be used only for components with a maximum height of 1.2mm.

#### 5.2.1 Pin assignment of module

The pin layouts of the D-Sub connector (or other frontpanel connector) and of the 24-pin receptacle connector are not defined.

5.2.2 Correspondence between 25-pin D-Sub connector and 24-pin peripheral connector

Figure 15 - Orientation of the 24-pin receptacle connector on the module

#### Recommendation

The 25-pin D-Sub connector is very common as a front panel peripheral connector for M-Modules. In principle, it is possible to connect different peripheral equipment signals via this connector and via the base board peripheral connector. However it is often desired to duplicate the signals. For this special - but very frequent - case, the correspondence between the two connectors is best implemented in a standard manner according to the following recommended scheme.

Table 6 - Recommendation for correspondence between 25-pin D-Sub connector and 24-pin peripheral connector

| 25-pin D-Sub |      | 24-pin receptacle connector |

|--------------|------|-----------------------------|

| receptacle   | plug |                             |

| 1            | 13   | 1                           |

| 2            |      | 3                           |

|              | 12   |                             |

| 3            | 11   | 5                           |

| 4            | 10   | 7                           |

| 5            | 9    | 9                           |

| 6            | 8    | 11                          |

| 7            | 7    | 13                          |

| 8            | 6    | 15                          |

| 9            | 5    | 17                          |

| 10           | 4    | 19                          |

| 11           | 3    | 21                          |

| 12           | 2    | 23                          |

| 13           | 1    | -                           |

| 14           | 25   | 2                           |

| 15           | 24   | 4                           |

| 16           | 23   | 6                           |

| 17           | 22   | 8                           |

| 18           | 21   | 10                          |

| 19           | 20   | 12                          |

| 20           | 19   | 14                          |

| 21           | 18   | 16                          |

| 22           | 17   | 18                          |

| 23           | 16   | 20                          |

| 24           | 15   | 22                          |

| 25           | 14   | 24                          |

#### 5.2.3 Electrical load

The electrical load on a connector pin depends on the plug component used, the receptacle component used and the printed wiring. No statements can be made about the front panel connector. As a rule, higher currents can be transmitted via the front panel connector than via the base board. The breakdown strength (and thus the isolation voltages for electrically isolated modules) is usually higher if the 24-pin receptacle connection is not used. The current permitted to flow via the base board peripheral connector is limited to 1A per pin. However, this does not guarantee that the base board can tolerate such high currents! The breakdown strength between 2 pins is min. 100V AC.

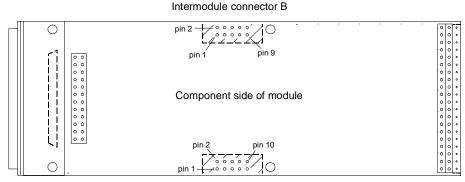

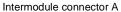

#### 5.3 Intermodule connections

A connection between one module and another may be necessary when several modules need to exchange data (for instance signal processors) without using the base board. Such connections are also desirable when modules are to be extended on the analog side - for instance A/D converters with multiplexers. The connection is made using two 10-pin connectors, arranged in such a way that it is possible to make a point-to-point connection from one module to the next using ribbon cable or plug adapter or to construct a bus connection joining several modules. In certain cases it is even possible to connect modules on different base boards using ribbon cable with plug connectors. Note that these connectors are necessary only for intermodule connections, and modules which do not require such connections can use the space for other components.

#### Figure 16 - Orientation of the 10-pin receptacle connectors on the module

#### 5.3.1 Pin assignment

The pin assignment of the 10-pin receptacle connector is not fixed. The use of intermodule connections is specific to the module; for instance, analog or digital intermodule connections may be implemented.

#### 5.3.2 Electrical specification

Since the scope of the intermodule specification is not fixed, the electrical characteristics cannot be defined. It should be pointed out that the reference ground for the signals could be line GND (i.e. the intermodule connection has an electrical connection to the base board), or it could be another potential isolated from the base board (for instance for analog multiplexers).

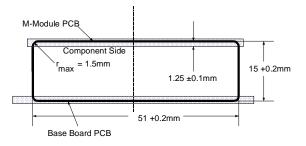

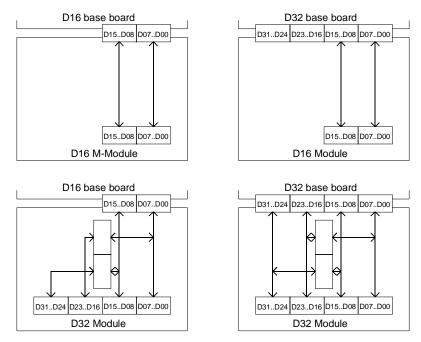

- 6 Mechanical specification

- 6.1 Dimensions of the modules

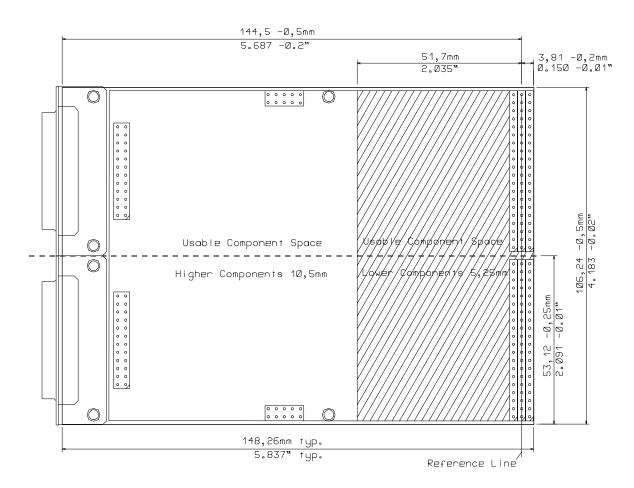

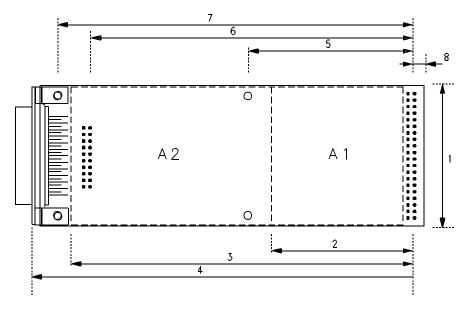

Figure 19 - Dimensions of a single MA-Module and position of connectors

Figure 20 - Example for mounting a single MA-Module on a base board

The reference line is drawn through the mid-points of the pins of the rightmost row of the plug header connector and not the outer edge of the printed circuit board.

An area of at least 20.6mm by 8.5mm shall be left free of other components in the area of the Intermodule Port connector to leave room for connectors from different suppliers, if such a connector is used.

Optimum utilization of volume is of great importance in the M-Module concept. Thus the modules are made as large as possible. Owing to the "sandwich construction" formed by the modules and the base board, the maximum height is, of course, less than for the base board alone.

In order to accommodate larger components, two component zones are defined, one for lower components (in an area where components may also be fitted on the base board) and one for higher components (in an area where only very flat components are allowed on the base board).

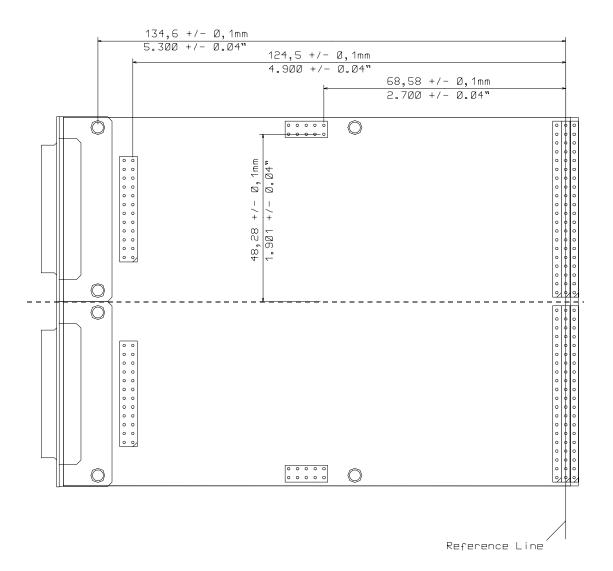

Figure 21 - Dimensions of a double MA-Module

Figure 22 - Position of connectors

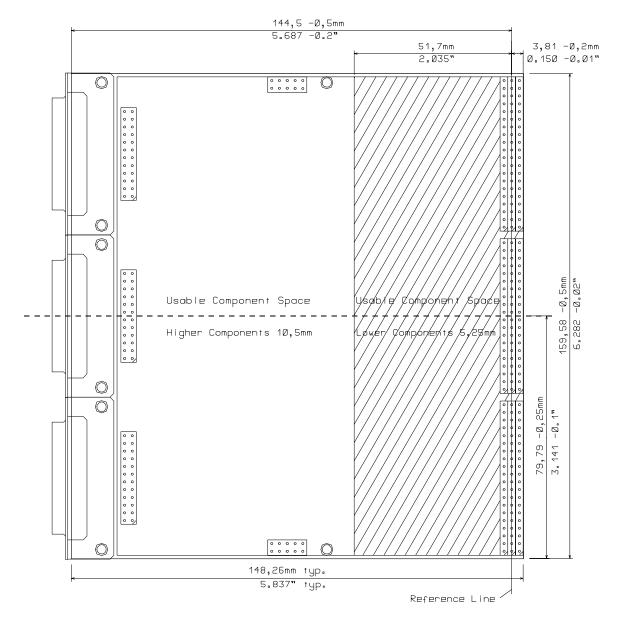

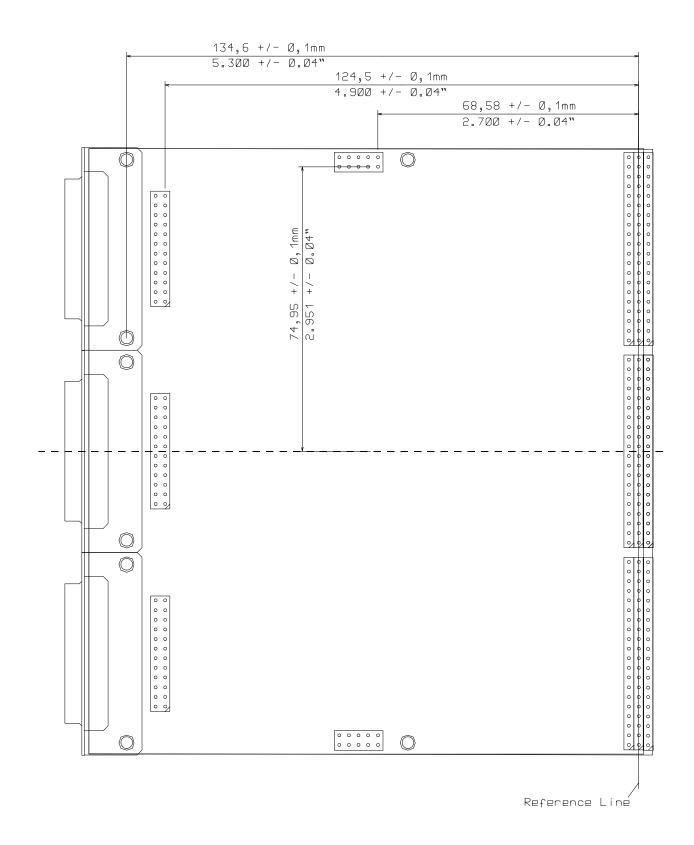

Figure 23 - Dimensions of a triple MA-Module

Figure 24 - Position of connectors

On the reverse side, the components may project by a maximum of **1.2mm** over the surface of the M-Module printed circuit board.

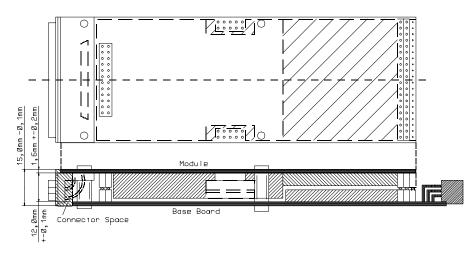

#### 6.2 Front panel of base boards

If the M-Module is mounted on a base board, it presumes that there is a gap for the front panel connector conforming to the following figure.

Figure 25 - M-Module front

Figure 26 - M-Module connectors

The connectors listed must correspond to figure  $26^{1}$ .

6.4 Mounting the M-Module on the base board

Four screws (DIN 85-M3x8) should be used with the module's hexagonal bolts for attaching the module to the printed circuit board.

10-pin ribbon cable plug connectors that can be used for the connecting cable of the intermodule connection are, e.g., the Scotchflex

printed circuit board connector 3910-2000T3M or compatible connectors.

#### Recommendation

Use the bolts to contact protective ground to the module to meet EMC requirements.

6.5 Resistance to mechanical shock and vibration

The modules must be able to withstand vibration of **1g** in the range **10..2000Hz** (2 cycles, duration: 30mn) according to IEC 68-2-6.

They must be able to withstand bumps of at least **25g** for **6ms** (half-sine) according to IEC 68-2-29.

They must be able to withstand a mechanical shock of at least **40g** for **6ms** (half-sine) according to IEC 68-2-27.

# 7 Thermal specification

The maximum power dissipation of a module must not exceed **10W**. Power may be supplied via the base board or via the peripheral connector.

All M-Modules must be fully operational at a temperature range of **at least 0..60^{\circ}C**. The permissible storage temperature range must be **-20..+70°C** or greater. Naturally, extended temperature ranges are conceivable for special operating conditions.

The air flow for cooling the module must be at least **4001 per hour**. The air temperature of the cooling air must not exceed the maximum ambient temperature of the module.

# Recommendation

CMOS components with low power dissipation should be given preference for use on M-Modules.

The standard humidity class according to DIN 40040 for all modules is: **F**, **non-condensing**.

<sup>1)</sup> Example of base board connection:

<sup>40-</sup>pin connectors that can be used for interface to the base board are, e.g.,

<sup>-</sup> BL6-40-Z (Fischer-Metroplast);

<sup>-</sup> AMP HV-100 series.

<sup>24-</sup>pin receptacle connectors that can be used for alternative peripheral connection via the base board are, e. g.,

BL6-24-Z (Fischer-Metroplast);

<sup>-</sup> BL6-24-Z (Fischer-Metrop

<sup>-</sup> AMP HV-100 series.

Example of peripheral connection:

<sup>25-</sup>pin D-Sub connector for peripheral connection:

<sup>-</sup> ZDF-25ABZKUNG (receptacle) Conec;

<sup>-</sup> ZDS-25ABZKUNG (plug) Conec.

These connectors have round screw bolts attached by rivet for strain relief.

<sup>10-</sup>pin receptacle connectors that can be used for intermodule connection are, e.g., MK2G-10 (Fischer-Metroplast) or compatible connectors.

## 8 Extended electrical specification

#### 8.1 Introduction

Four main requirements led to this extension to the M-Module specification:

- extension of the address bus to a maximum of 24 bits, allowing up to 16 Mbytes to be addressed;

- extension of the data bus width to 32 bits;

- provision for trigger signals for measurement applications, e.g. for use in VXIbus systems;

- burst access for higher data rates.

Modules with these capabilities need additional signals for communication with the base board and this requires additional pins. M-Modules with a 3-row, 60-pin baseboard interface connection are termed MA-Modules. The design of the base board enables M-Modules and MA-Modules to be mixed. This presents no problems if certain restrictions are borne in mind. Base boards with only a 2-row, 40-pin connection normally cannot utilize all features of an MA-Module (trigger features for instance). Nevertheless, it is often possible to operate an MA-Module on a base board for M-Modules. At all events, any M-Module or MA-Module can be operated on base boards designed for MA-Modules.

#### 8.1.1 Extended address space

The extended address space enables M-Modules to be used for applications extending beyond typical I/O functions. The address space can be extended so as to have M-Modules with a 24-bit address bus. When choosing a base board it is merely necessary to ensure that the address space of the base board is at least as large as the address space of the M-Module. If not, there may be restrictions on the operation of the module, but such a combination may be justified for some modules. If the base board is not able to supply all 23 lines for a 24-bit address bus, the unsupplied lines shall be driven to "low".

The address information is transferred across the data bus in multiplexed mode, reducing the number of pins required. An additional line - /AS - indicates the current use of the bus. The normal M-Module store cycle is embedded in the address transfer cycle. The high-order (most significant) address information is transferred at the beginning of a cycle while /AS is at "H" potential. The module can store this information at the falling edge.

During the following data transfer cycle (which is completely compatible with the basic electrical specification), /AS functions as an address modifier. If /AS is "H" the access is what is now termed an I/O access, using the 256-byte address space. However, if /AS is "L" - i.e. a falling edge has occurred and the

high-order part of the address has been transferred across the data bus - it is what is now termed a memory access.

This permits construction of modules with a 16-Mbyte memory area and a 256-byte I/O area.

One such application could be a graphics module, where any base board - including base boards with an 8-bit address bus - can access the I/O area and a base board with a 24-bit address bus can also access video memory directly.

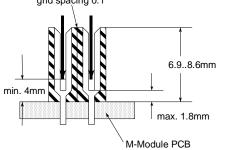

8.1.2 32-bit data bus

The data bus extension is implemented using 16 pins from the third row. This true parallel 32-bit data bus allows M-Modules to be optimized for maximum data transfer rates.

An additional control line is used to provide the necessary dynamic bus sizing. This permits 32-bit M-Modules to be used on a base board with a 16-bit data bus. The dynamic bus sizing is also compatible with dynamic buses such as the VMEbus or the bus used by Intel's 80486 microprocessor.

The extension is primarily aimed at increasing data throughput. The increase in the width of the data bus can be seen as completely independent of the address bus extension (for instance for controlling fast FIFOs with a width of 32 bits, which do not require an extended address space).

8.1.3 Burst access

Burst access serves for fast data exchange between the base board and an M-Module. Burst access can be applied with all addressing modes (A08 and A24).

#### 8.1.4 Trigger lines

The universal trigger lines can be used for any kind of synchronization between M-Modules or for synchronization of M-Modules with the base board.

/AS

Two pins are provided for this purpose. They must always be inputs following M-Module reset in order to guarantee compatibility between different M-Modules and base boards.

Typical applications are multichannel analog-to-digital converters which must sample at exactly the same time.

- 8.2 Communication between M-Module and base board

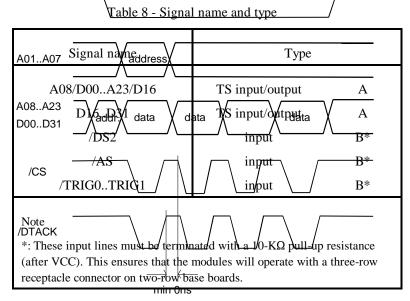

- 8.2.1 Signals

- D00/A08..D15/A23 Multiplexed data/address bus. When line /AS is at "H" potential, the most significant bits of the address can be transmitted using these lines. They must be stored by the module at the falling edge of /AS. Thereafter these lines form the bidirectional data bus as defined in the basic electrical specification.

- D16..D31 Most significant portion of the bidirectional data bus. D16 is the least significant data bit and D31 is the most significant bit. It should be stressed here that this does not specify any byte order, merely a bit order and an identification of the bytes.

If the M-Module has only an 8bit data bus, only D00..D07 shall be used, a 16-bit module must use D00..D15.

MSB D31..D24 D23..D16 D15..D08 D07..D00 LSB

Figure 27 - Bit order

Input signal. Address strobe. Indicates the meaning of the signals on the multiplexed address/data bus. If /AS is "H", address information can be transmitted via lines D00/A08..D15/A23. The M-Module must store the address at the falling edge. While /CS asserted ("L"), is /AS functions as an address modifier: if /AS is "L", the access is to the extended address range; if /AS is "H", an access in I/O mode is performed.

- /DS0..2 Input signals. They are valid while /CS, /IACK or /DACK is active. Together with A1 the three data-select lines specify whether the access is a byte, 2byte or 4-byte access. Also, for byte access or 2-byte access the data routing, i.e. the active part of the data bus and the data specified. flow, is The following figure and table show the meaning of the signals. TRIGA, TRIGB

- Trigger inputs/outputs. After power-up these lines must always be inputs. During operation they can be programmed under software control as outputs. It is possible to trigger specific actions on the M-Modules at the positive edge. If only one trigger line is used it must be TRIGA.

Figure 28 - Data bus routing

| /DS2 | /DS1 | /DS0 | A1 | M-Module<br>interface | D32<br>M-Module | D16<br>M-Module |       |

|------|------|------|----|-----------------------|-----------------|-----------------|-------|

|      |      |      |    |                       | internal        | internal        |       |

| Н    | Н    | Н    | L  | -                     | -               | -               |       |

| Н    | Н    | L    | L  | D00D07                | D16D23          | D00D07          |       |

| Н    | L    | Н    | L  | D08D15                | D24D31          | D08D15          | D16/  |

| Н    | L    | L    | L  | D00D15                | D16D31          | D00D15          | D32   |

| Н    | Н    | Н    | Н  | -                     | -               | -               | base  |

| Н    | Н    | L    | Н  | D00D07                | D00D07          | D00D07          | board |

| Н    | L    | Н    | Н  | D08D15                | D08D15          | D08D15          |       |

| Н    | L    | L    | Н  | D00D15                | D00D15          | D00D15          |       |

|      |      |      |    |                       |                 |                 |       |

| L    | Н    | Н    | L  | D00D31                | D00D31          | -               |       |

| L    | Н    | L    | L  | D16D23                | D16D23          | -               |       |

| L    | L    | Н    | L  | D24D31                | D24D31          | -               | D32   |

| L    | L    | L    | L  | D16D31                | D16D31          | -               | base  |

| L    | Н    | Н    | Н  | D00D31                | D00D31          | -               | board |

| L    | Н    | L    | Н  | D00D07                | D00D07          | D00D07          |       |

| L    | L    | Н    | Н  | D08D15                | D08D15          | D08D15          |       |

| L    | L    | L    | Н  | D00D15                | D00D15          | D00D15          |       |

Table 7 - Data bus routing

- 8.2.2 Principles of operation

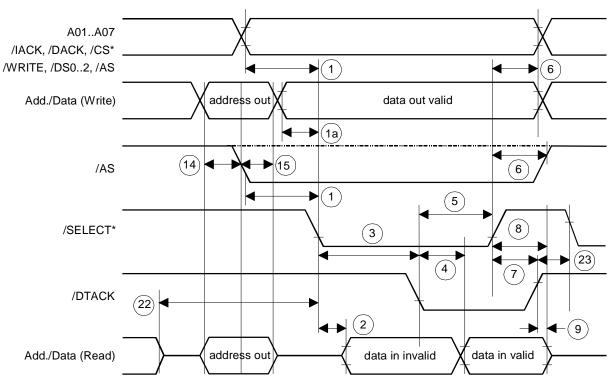

- 8.2.2.1 Read/write access no burst

The normal M-Module access cycle is embedded in the address transfer cycle. At the beginning of one of these accesses, while /AS is at "H" potential, the most significant address information is transferred. On the falling edge the module can store the information. The address information is transferred over the data bus in multiplexed mode.

The actual access cycle is in accordance with the basic

Figure 29 - Signal sequence of a read/write access

electrical specification.

#### 8.2.2.2 Burst access

A burst transfer cycle starts with a normal access cycle (read or write) involving both address and data transfers. This first cycle is followed by an arbitrary number of cycles involving data transfers only.

An M-Module with burst mode capability must implement an internal address generator which is loaded with the start address during the first (address/data cycle) and must generate follow-on addresses for the data cycles in the remainder of a burst transfer. This address generator must at least provide two features: (1) linear up and down counting and (2) wrap around modulo a fixed length of the address range covered. It may of course provide additional features such as programmable address range, more sophisticated address sequencing such as "reverse carry" etc.

The first cycle of a burst transfer must always be an A24 access differing in no aspect from a normal (non-burst) access. The module has to pick up the start address combined from A1..A7 and multiplexed A8..A23 in a look-ahead fashion, regardless if the following cycle continues with data bursts or not. The /AS signal is kept low after the address/data cycle and during all data cycles in the burst. This can easily be decoded by the module for internal control of burst transfers.

Data transfers within a burst are handshaked by /CS (or linked to that, change of data) and /DTACK. Suitable timing of the leading (falling) edge of /DTACK ensures that the module's access time is met. Timing of the trailing (rising) edge forces the base board not to start with the next cycle before the module has completed the on-going transfer. For that reason, the only extension of timing specifications is that in consecutive cycles during a burst, /CS must go low 0ns after /DTACK has been de-asserted at the earliest. All other timing relationships are retained and can be taken over from the basic electrical specification.

The figure below illustrates a burst transfer sequence for write transfers. Read transfers are similar, the timing can be derived from the basic electrical specification. The data direction cannot change during a burst. The status of the /WRITE signal can be latched in the first cycle.

# 8.2.3 Driver characteristics

Figure 30 - Burst transfer sequence for write transfers The electrical specification of the drivers over the whole

temperature range is given in table 3 in the basic electrical specification.

The capacitive load of a pin must not exceed 25pF.

8.2.4 Timing specifications

Regardless of the minimum specification, the appropriate data sheets for the modules must be compared in order to ensure that the maximum trigger rates and maximum frequencies of modules and base boards are compatible.

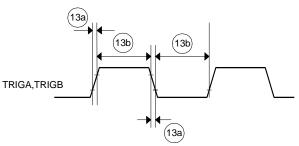

Figure 31 - TRIGA and TRIGB timing

#### NOTE

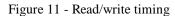

\*: "/SELECT" represents one of the three signals /CS, /DACK or /IACK. Only one of these (designated "/SELECT") is asserted ("L") during a cycle; the others are "H" as indicated in the following table.

| Cycle type            | /CS | /DACK | /IACK |

|-----------------------|-----|-------|-------|

|                       |     |       |       |

| Normal access         | L   | Н     | Н     |

| DMA access            | Н   | L     | Н     |

| Interrupt acknowledge | Н   | Н     | L     |

|                       |     |       |       |

Figure 32 - Read/write timing

Table 9 - Timing parameters

| Num | Characteristic                  | Min | Max | Unit |

|-----|---------------------------------|-----|-----|------|

| 13a | TRIGA, TRIGB rise and fall time | -   | 20  | ns   |

| 13b | TRIGA, TRIGB hold time          | 7   | -   | ns   |

| 14  | Address setup                   | 10  | -   | ns   |

| 15  | Address hold                    | 10  | -   | ns   |

# 8.2.5 Pin assignment

The control interface between the base board and the module is via three-row plug connectors (pin headers) on the base board, which correspond to receptacles on the module.

Rows A and B are in accordance with the pin assignments described in the basic electrical specification. Row C is additional.

| Pin | Row A   | Row B   | Row C |

|-----|---------|---------|-------|

|     |         |         |       |

| 1   | /CS     | GND     | /AS   |

| 2   | A01     | +5V     | D16   |

| 3   | A02     | +12V    | D17   |

| 4   | A03     | -12V    | D18   |

| 5   | A04     | GND     | D19   |

| 6   | A05     | /DREQ   | D20   |

| 7   | A06     | /DACK   | D21   |

| 8   | A07     | GND     | D22   |

| 9   | D08/A16 | D00/A08 | TRIGA |

| 10  | D09/A17 | D01/A09 | TRIGB |

| 11  | D10/A18 | D02/A10 | D23   |

| 12  | D11/A19 | D03/A11 | D24   |

| 13  | D12/A20 | D04/A12 | D25   |

| 14  | D13/A21 | D05/A13 | D26   |

| 15  | D14/A22 | D06/A14 | D27   |

| 16  | D15/A23 | D07/A15 | D28   |

| 17  | /DS1    | /DS0    | D29   |

| 18  | /DTACK  | /WRITE  | D30   |

| 19  | /IACK   | /IRQ    | D31   |

| 20  | /RESET  | SYSCLK  | /DS2  |

| 10 - Pin assignmen | ssignment | Pin | 10 - | Table |

|--------------------|-----------|-----|------|-------|

| 10 - Pin assignmen | ssignmen  | Pin | 10 - | Table |

Figure 33 - Orientation of the receptacle connector on the module

# Annex A

# (informative)

# Driver software interface

# Revision 1

## A.1 Introduction

This annex specifies a software interface for M-Modules in accordance with the hardware specifications.

The interface has been designed in such a way that all hardware functions of an M-Module can be controlled by means of eight defined driver functions (plus an interrupt handler). In this specification the functions of this interface are referred to as low-level driver (LL driver).

Usually, a higher software layer is added to the LL driver. In this specification the functions of this layer are referred to as high-level driver (HL driver).

By means of pre-defined service functions that must be provided by an HL driver, it is possible to trigger the HL driver functions from the LL driver. This includes system-specific functions and buffer management functions.

The interface described here has been implemented in the "C" programming language.

The LL driver can be used as follows:

- as an LL driver: part of an MDIS driver;

- as an LL driver: part of one's own driver developments;

- as a function library: direct hardware access from an application.

#### A.2 Definitions

#### A.2.1 Device

A device is a physical unit (M-Module). Each device is described by a structure, the descriptor structure. This structure contains all the physical and logical parameters of the device.

Within a system, a device is uniquely identified by its base address, i.e. there must not be more than one device with this base address.

# A.2.2 Channel

An M-Module is a device with one or more physical channels. Each channel is characterized by a specific channel width (in bits), transmission direction, and type. The number of channels of a device is limited to 256.

A.3 Remarks concerning the highlevel driver

## A.3.1 Functions

The definition of the LL interface is based on the following proposed HL driver functions:

- system initialization and interrupt installation;

- device initialization and de-initialization;

- read and write accesses to the device;

- allocation and management of an input buffer or output buffer or both;

- read and write accesses to the input/output buffers;

- handling of events via signals.

The above-mentioned functions are only a proposal. Apart from the defined service functions, implementation of the HL driver is left completely to the user.

#### A.3.2 Descriptor structure

Each device driver must be able to operate one or several devices of the same kind. For this purpose, each device is referenced by means of a structure referred to here as a descriptor structure. The descriptor structure contains all physical and logical attributes of a device (e.g. number and description of channels). Additional data structures required by the HL driver to manage the device may be part of the descriptor structure.

The descriptor structure is managed by the HL driver and passed to the LL functions as a pointer.

Some elements of the descriptor structure are available to the LL driver for read or write access. Accessing those elements must be done by means of macros (see A.7). Therefore, the descriptor structure must contain at least the elements which are available to the LL driver.

The exact descriptor structure depends on the implementation of the HL driver and is not part of this specification.

#### A.3.3 The device options field

Some LL drivers require an additional data area for storing global device data, referred to here as the device options field.

To access this area, the **OPT\_PTR** is provided for in the descriptor structure. It can point to any kind of data block, the size of which is defined in **OPT\_LEN**.

The HL driver must allocate a memory area of the size determined and enter the starting address in the descriptor parameter (**OPT\_PTR**). The device options field must be allocated separately for each device.

The LL driver does not check whether or not a device options field exists.

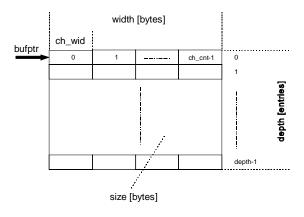

#### A.3.4 I/O buffer management

The HL driver has the task of allocating, providing and managing an input buffer or output buffer or both. It provides the LL driver with one service function each for requesting and terminating buffer entries. When requesting, the LL driver is supplied with a buffer entry. The termination function signals the HL driver that the buffer entry is terminated. Then the HL driver can update its buffer pointers and wake up waiting processes.

#### A.3.5 Handling of events

An LL driver can support up to 4 events, referred to here as signal conditions. These are used for signaling a process (user program) via a software interrupt that certain events are occurring on the device.

When a signal condition is activated or de-activated by the HL driver, this is signaled to the LL driver by the setstat routine being called. When activating (code: SIG\_set\_cond?), the driver must initialize the hardware in such a way that the signal condition can trigger an interrupt. When de-activating (code: SIG\_clr\_cond?), the driver must initialize the hardware in such a way that the signal condition cannot trigger an interrupt.

The HL driver provides the LL driver with a service function for handling the signal conditions. If such an event occurs in the form of an interrupt, the LL driver must signal this event to the HL driver by calling the **M\_sig\_cond**() service function. This makes it possible for the HL driver to trigger a software interrupt, e.g. in the form of a signal.

#### A.3.6 Interface to the LL driver

The interface to the LL driver is designed in such a way that this driver only has to carry out basic input or output actions to a device, e.g. "read channel 2 from device to base address 0xffe00000". The LL driver is freed from any other tasks, such as system initialization, interrupt installation, buffer management, memory allocation (buffer), etc.

The HL driver ensures that all function parameters passed to the LL driver are valid. The LL routines in turn must terminate with defined return values in order to signal the HL driver whether an action has been successful or not.

# A.4 Driver functions of the low-level driver

#### A.4.1 Survey

An LL driver has the following entry points (functions):

- **<dev>\_init**() initialize device;

- <dev>\_exit()

de-initialize device;

- <dev>\_read()

read from one channel of the device;

| · · · · · ·                            |                                                  |

|----------------------------------------|--------------------------------------------------|

| <pre>- <dev>_write()</dev></pre>       | write to one channel of the device;              |

| <pre>- <dev>_block_read()</dev></pre>  | read all (input) chan-<br>nels of the device;    |

| <pre>- <dev>_block_write()</dev></pre> | write all (output)<br>channels of the<br>device; |

| - <dev>_setstat()</dev>                | set device para-<br>meters;                      |

| - <dev>_getstat()</dev>                | get device para-<br>meters;                      |

| - <dev>_irq_c()</dev>                  | interrupt handler.                               |

<dev> is the device name (e.g. device "xyz": xyz\_init(), xyz\_exit()).

# A.4.2 Device initialization

| Call       | Bit32 <dev>_init(mod_ptr,ch,base,mode)</dev>                |                                                                                        |

|------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Parameters | MODUL_DATA *mod_ptr<br>Bit32 ch<br>Bit32 base<br>Bit32 mode | pointer to descriptor structure<br>channel number (0255)<br>base address<br>(not used) |

| Returns    | 0<br>err(code)                                              | if OK<br>if an error occurred                                                          |

The init routine is called by the HL driver for initialization of the device. System initialization must be carried out beforehand. In addition, the device options field must be available if required.

The routine has the task of putting the device with the base address **base** into a defined initial condition, i.e. carrying out a hardware reset on all channels. The **ch** parameter defines the channel selected after the reset. In most cases, this parameter can be ignored.

Possible errors:

| ERR_Init     | general initialization error |  |

|--------------|------------------------------|--|

| ERR_IllParam | illegal parameter            |  |

# A.4.3 Device de-initialization

| Call       | Bit32 <dev>_exit(mod_ptr,ch,base,mode)</dev>                |                                                                                        |

|------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Parameters | MODUL_DATA *mod_ptr<br>Bit32 ch<br>Bit32 base<br>Bit32 mode | pointer to descriptor structure<br>channel number (0255)<br>base address<br>(not used) |

| Return     | 0<br>err(code)                                              | if OK<br>if an error occurred                                                          |

The exit routine is called by the HL driver in order to de-initialize the device. System de-initialization may be carried out only after this.